Universidade de Brasília - UnB Faculdade UnB Gama - FGA Engenharia Eletrônica

## Implementação em FPGA da Camada Convolucional de um Algoritmo de Redes Neurais para um Módulo Estimador da Frequência Cardíaca Fetal

Autor: Misael de Souza Andrade

Orientador: Prof. Dr. Gilmar Silva Beserra

Brasília, DF 2022

#### Misael de Souza Andrade

## Implementação em FPGA da Camada Convolucional de um Algoritmo de Redes Neurais para um Módulo Estimador da Frequência Cardíaca Fetal

Monografia submetida ao curso de graduação em (Engenharia Eletrônica) da Universidade de Brasília, como requisito parcial para obtenção do Título de Bacharel em (Engenharia Eletrônica).

Universidade de Brasília - UnB Faculdade UnB Gama - FGA

Orientador: Prof. Dr. Gilmar Silva Beserra

Coorientador: Prof. Dr. Daniel Mauricio Muñoz Arboleda

Brasília, DF 2022

Misael de Souza Andrade

Implementação em FPGA da Camada Convolucional de um Algoritmo de Redes Neurais para um Módulo Estimador da Frequência Cardíaca Fetal/ Misael de Souza Andrade. – Brasília, DF, 2022-

95 p. : il. (algumas color.) ; 30 cm.

Orientador: Prof. Dr. Gilmar Silva Beserra

Trabalho de Conclusão de Curso – Universidade de Brasília - UnB Faculdade UnB Gama - FGA , 2022.

1. Redes Neurais. 2. FPGA. I. Prof. Dr. Gilmar Silva Beserra. II. Universidade de Brasília. III. Faculdade UnB Gama. IV. Implementação em FPGA da Camada Convolucional de um Algoritmo de Redes Neurais para um Módulo Estimador da Frequência Cardíaca Fetal

#### Misael de Souza Andrade

## Implementação em FPGA da Camada Convolucional de um Algoritmo de Redes Neurais para um Módulo Estimador da Frequência Cardíaca Fetal

Monografia submetida ao curso de graduação em (Engenharia Eletrônica) da Universidade de Brasília, como requisito parcial para obtenção do Título de Bacharel em (Engenharia Eletrônica).

Trabalho aprovado. Brasília, DF, 12 de maio de 2022:

Prof. Dr. Gilmar Silva Beserra Orientador

Prof. Dr. Daniel Mauricio Muñoz Arboleda Co-Orientador Convidado 1

Prof. Dr. Daniel Chaves Café

Examinador

Convidado 2

Brasília, DF 2022

## Agradecimentos

Agradeço em primeiro lugar, a Deus, pela minha vida, e por me permitir ultrapassar todos os obstáculos encontrados ao longo da realização deste trabalho. Aos meus pais, que por meio de muito trabalho, esforço e amor me deram a oportunidade de chegar até aqui. A minha esposa que me incentivou e apoiou nos momentos difíceis e compreendeu a minha ausência enquanto eu me dedicava à realização deste trabalho. Por fim, ao meu orientador e a todos os professores do curso, por sua dedicação, paciência e conhecimento.

## Resumo

A necessidade de identificar padrões em sinais com alta confiabilidade vem crescendo de forma exponencial, devido à enorme quantidade de dados dispostos no mundo atual. A aplicação de Redes Neurais Artificiais para atingir esse objetivo é crescente e a redução no custo de implantação é constante à medida em que se popularizam ferramentas computacionais que permitem a inserção de novas técnicas para solução de problemas complexos. Devido ao alto custo computacional da implementação das redes neurais, torna-se necessária a abordagem de aceleração de algoritmos com FPGA (Field Programmable Gate Arrays, onde a parte com maior exigência de processamento é executada em hardware. Por meio deste embasamento, este trabalho apresenta o conceito de aceleração de algoritmos por meio da implementação em FPGA da primeira camada convolucional de uma Rede Neural Convolucional, que estima o ECG fetal (fECG) em um sinal de ECG abdominal (aECG). O projeto da camada convolucional em FPGA mostrou-se 5.85 vezes mais rápido do que o modelo em software executado no microprocessador ARM-Zynq. Também foi avaliado a eficiência de cálculo da convolução, que mostrou um um erro médio quadrático calculado de apenas 0.000123 para os resultados entre hardware e software, usando uma representação aritmética de ponto flutuante de 27 bits e 32 bits, respectivamente. Os resultados satisfatórios obtidos neste trabalho confirmam a importância da aceleração em hardware de algoritmos de redes neurais convolucionais.

Palavras-chave: fECG. Redes Neurais. CNN. VHDL. FPGA. Aceleração de algoritmos. SoC.

## **Abstract**

The need to identify patterns in signals with high reliability has been growing exponentially, due to the huge amount of data available in the current world. The application of Artificial Neural Networks to achieve this goal is increasing and the reduction in the cost of implementation is constant as computational tools are popularized that allow the insertion of new techniques to solve complex problems. Due to the high computational cost of implementing neural networks, it is necessary to approach algorithms with FPGA (Field Programmable Gate Arrays), where the part with the highest processing demand is executed in hardware., this work presents the concept of algorithm acceleration through the FPGA implementation of the first convolutional layer of a Convolutional Neural Network, which estimates the fetal ECG (fECG) in an abdominal ECG signal (aECG). FPGA proved to be 5.85 times faster than the software model run on the ARM-Zyng microprocessor. The convolution calculation efficiency was also evaluated, which showed a calculated mean square error of only 0.000123 for the results between hardware and software, using a 27-bit and 32-bit floating point arithmetic representation, respectively. The satisfactory results obtained in this work confirm the importance of ia of hardware acceleration of convolutional neural network algorithms.

Key-words: fECG. Neural Network. CNN. VHDL. FPGA. Algorithm acceleration. SoC.

# Lista de ilustrações

| Figura 1 –  | Sistema de aquisição aECG e extração do fECG para estimativa do FHR. FONTE: (JAGANNATH; SELVAKUMAR, 2014)                                                                                                                        | 22 |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figura 2 –  | Protótipo de sistema para estimativa da FHR através da aquisição de                                                                                                                                                              | -  |

|             | sinais aECG. Em desenvolvimento pela Universidade de Brasília - FGA.                                                                                                                                                             | 23 |

| Figura 3 –  | Estágios de desenvolvimento do coração fetal de (a) a (f): a)tubos endo-<br>cárdicos. b)comunicações entre tubos endocárdicos. c) arcos aórticos,<br>sacos aórticos, mioepicárdio, átrios e seios venosos d)arcos aórticos, bul- |    |

|             | bus cordis, ventríloco e átrio e)arcos aórticos I, arcos aórticos II, átrios primitivos, ventrílocos primitivos f)veia cava superior, aorta, tronco                                                                              |    |

|             | pulmonar, átrios, ventrílocos, veia cava inferior. FONTE: (SAMENI; CLIFFORD, 2011)                                                                                                                                               | 25 |

| Figura 4 –  | O ciclo de ativação do coração fetal. FONTE: (SAMENI; CLIFFORD,                                                                                                                                                                  | 26 |

| T. *        | 2011)                                                                                                                                                                                                                            | 26 |

| Figura 5 –  | Ilustração dos sistemas de extração AES e CS. FONTE: (KAHAN-KOVA et al., 2020)                                                                                                                                                   | 27 |

| Figura 6 -  | Composição de um neurônio biológico. FONTE: (BRITO, 2019)                                                                                                                                                                        | 28 |

| Figura 7 –  | Modelo não linear de um neurônio. FONTE: (HAYKIN, 2001)                                                                                                                                                                          | 29 |

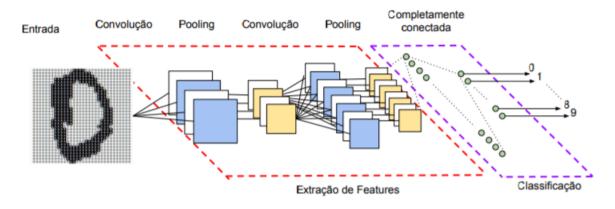

| Figura 8 –  | Modelo de uma rede neural convolucional e suas diferentes camadas.  FONTE: (VARGAS; CARVALHO; VASCONCELOS, 2016)                                                                                                                 | 30 |

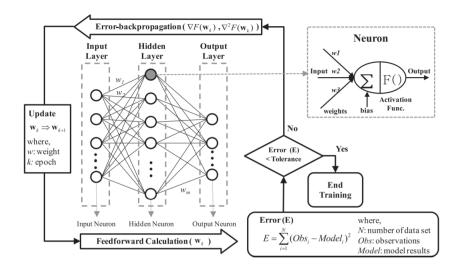

| Figura 9 –  | Diagrama esquemático do algoritmo de treinamento de retropropagação e modelo de neurônio típico. FONTE: (KIM; SEO, 2015)                                                                                                         | 32 |

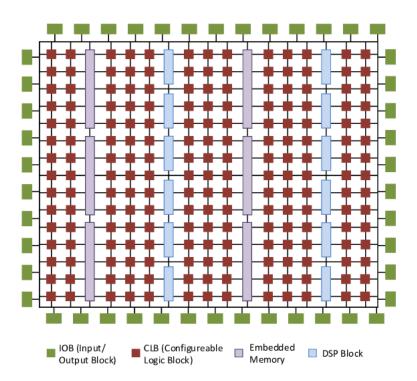

| Figura 10 – | Arquitetura interna de um chip FPGA típico. FONTE: (BAJAJ; FAHMY, 2015)                                                                                                                                                          | 33 |

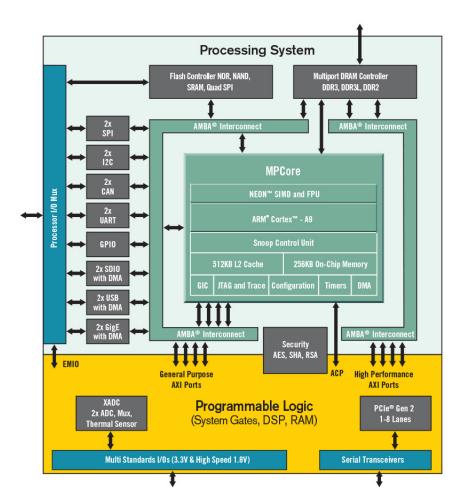

| Figura 11 – | Diagrama de Blocos estrutural do Zynq-7000 Soc. FONTE:(XILINX,                                                                                                                                                                   | 35 |

| Figura 12 - | Vivado Design Suite IP Flow. FONTE: Adaptado de (FEIST, 2012)                                                                                                                                                                    | 41 |

|             |                                                                                                                                                                                                                                  | 41 |

| Figura 14 - | comunicação Host-Target para o xSDK. FONTE:(XILINX, 2019)                                                                                                                                                                        | 42 |

| _           |                                                                                                                                                                                                                                  | 43 |

|             | •                                                                                                                                                                                                                                | 45 |

| Figura 17 - | Sinal aECG final gerado no MatlLab. Fonte: Autor                                                                                                                                                                                 | 46 |

|             |                                                                                                                                                                                                                                  | 47 |

| <u> </u>    | Diagrama de blocos do microprocessador ARM-Zynq instanciado como                                                                                                                                                                 |    |

|             | · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                            | 48 |

| Figura 20 – | Cógido em C para a primeira camada convolucional. [numberOfFilters=32; sampleLength=60; firstFilterLength=7.] FONTE: Adaptado                                                                                 |            |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

|             | de (JUNIOR, 2018)                                                                                                                                                                                             | 49         |

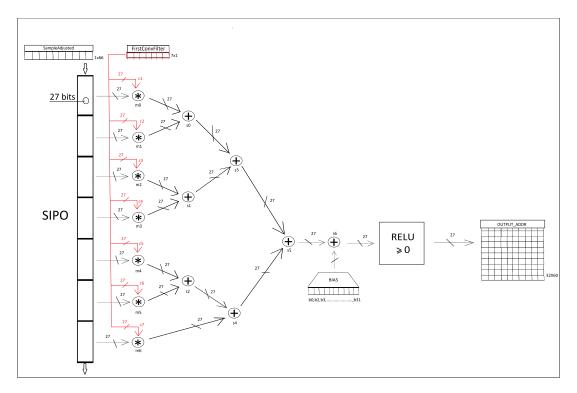

| Figura 21 – | Arquitetura proposta para iteração do loop interno da primeira camada                                                                                                                                         |            |

|             | convolucional. FONTE: Autor.                                                                                                                                                                                  | 51         |

| Figura 22 – | Esquemático RTL do bloco do loop interno da convolução descrito em VHDL com 7 multiplicadores, 7 somadores e registradores para saída. A disposição dos blocos foi definida pela ferramenta do Vivado. FONTE: |            |

|             |                                                                                                                                                                                                               | <b>5</b> 1 |

| D: 00       | Autor.                                                                                                                                                                                                        | 51         |

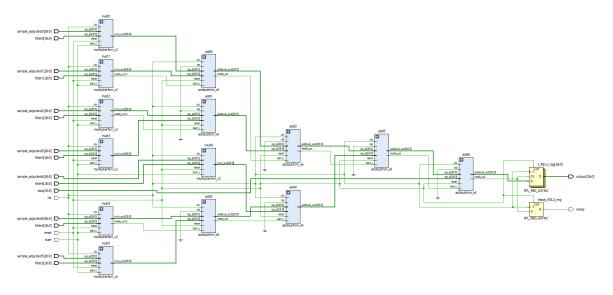

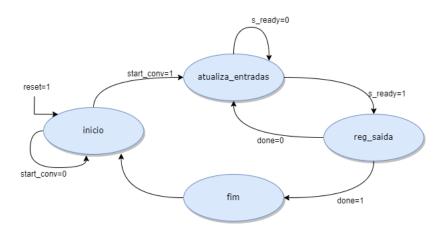

| Figura 23 – | Diagrama de blocos da FSM descrita em VHDL utilizando 3 processos.                                                                                                                                            |            |

|             | FONTE: Autor                                                                                                                                                                                                  | 52         |

|             | Diagrama de estados simplificado da FSM. FONTE: Autor                                                                                                                                                         | 53         |

|             | Diagrama de blocos do módulo principal. FONTE: Autor                                                                                                                                                          | 54         |

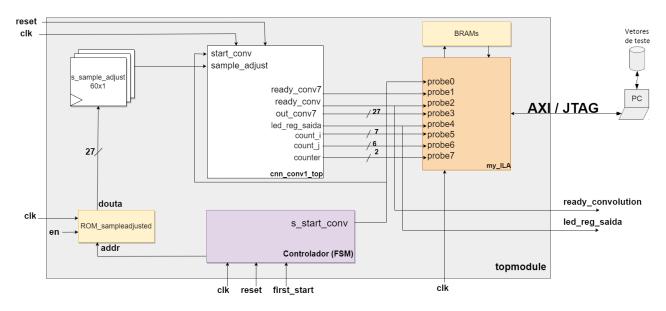

| Figura 26 – | Diagrama de blocos do topmodule com instanciação do ILA core, ca-                                                                                                                                             |            |

|             | mada convolucional, BRAM e FSM para controle. FONTE: Autor                                                                                                                                                    | 54         |

| Figura 27 – | Análise de <i>profiling</i> da CNN com o <i>gprof</i> no ARM-Zynq. FONTE: Autor.                                                                                                                              | 55         |

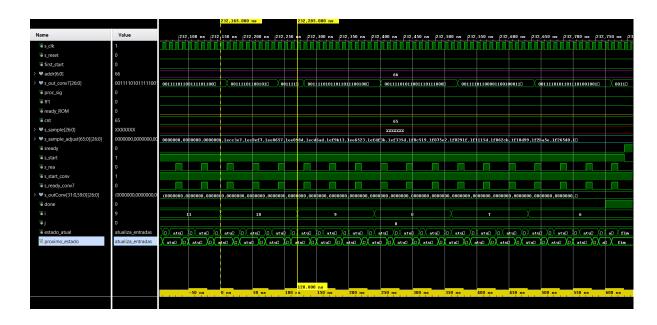

| Figura 28 – | Simulação comportamental do bloco do loop interno da convolução:                                                                                                                                              |            |

|             | conv7samples. FONTE: Autor.                                                                                                                                                                                   | 57         |

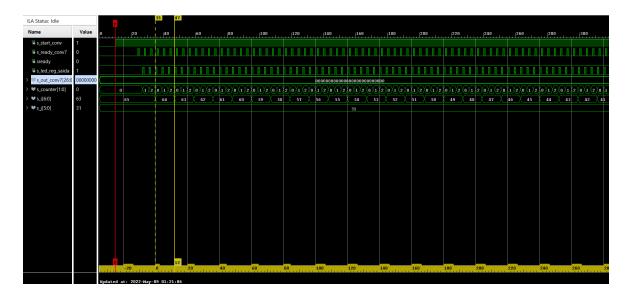

| Figura 29 – | Simulação comportamental do módulo principal:registro dos resultados                                                                                                                                          |            |

|             | da camada convolucional na matriz de saída 60x32. FONTE: Autor                                                                                                                                                | 58         |

| Figura 30 - | Simulação comportamental do módulo principal:transição dos estados                                                                                                                                            |            |

|             | e contadores de índices matriciais i e j. FONTE: Autor                                                                                                                                                        | 59         |

| Figura 31 – | Funcionamento da leitura e registro temporário das 66 amostras de                                                                                                                                             |            |

|             | entrada da primeira camada convolucional. FONTE: Autor                                                                                                                                                        | 59         |

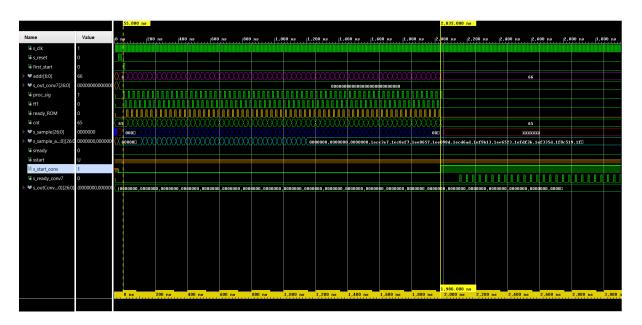

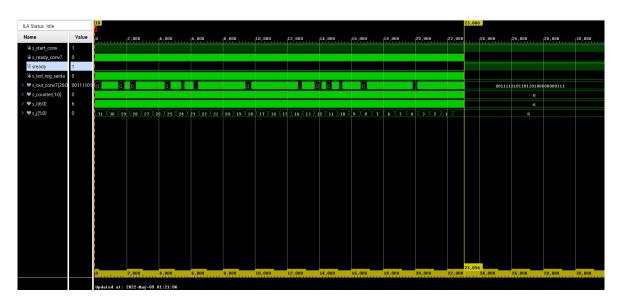

| Figura 32 – | Implementação da primeira camada convolucional com testes pelo ILA                                                                                                                                            |            |

|             | Core. Tempo geral da convolução. FONTE: Autor                                                                                                                                                                 | 60         |

| Figura 33 – | Implementação da primeira camada convolucional com testes pelo ILA                                                                                                                                            |            |

|             | Core. Tempo de saída de resultado da convolução. FONTE: Autor                                                                                                                                                 | 61         |

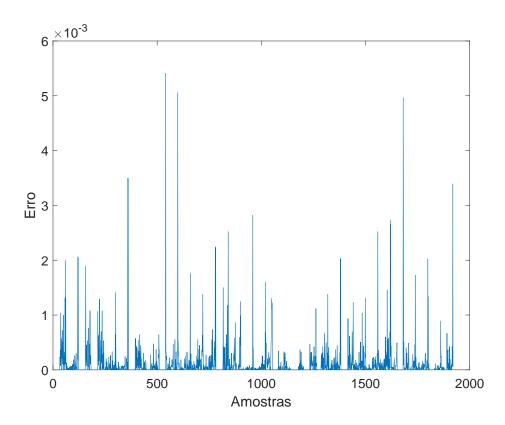

| Figura 34 – | Distribuição de erro numérico para os resultados da primeira camada                                                                                                                                           |            |

|             | convolucional implementada em hardware, utilizando FPU de 27 bits.                                                                                                                                            |            |

|             | FONTE: Autor                                                                                                                                                                                                  | 62         |

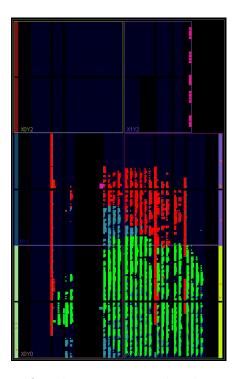

| Figura 35 – | Representação gráfica dos recursos utilizados no FPGA da Basys3 para                                                                                                                                          | -          |

| 1.6010 00   | implementação do circuito + ILA. FONTE: Autor                                                                                                                                                                 | 62         |

| Figura 36 – | Report de utilização de recursos pelo circuito. FONTE: Autor                                                                                                                                                  | 63         |

|             | Report de consumo de energia da Basys3 pelo circuito + ILA. FONTE:                                                                                                                                            | 00         |

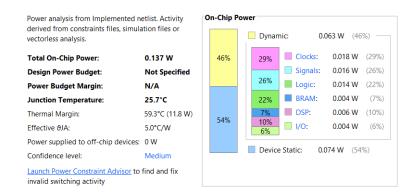

| 1 18414 01  | Autor                                                                                                                                                                                                         | 63         |

| Figure 38   | Report de <i>timing</i> do circuito implementado no FPGA + ILA. FONTE:                                                                                                                                        | UJ         |

| rigura 30 – |                                                                                                                                                                                                               | 63         |

|             | Autor                                                                                                                                                                                                         | 00         |

## Lista de tabelas

## Lista de abreviaturas e siglas

FHR Fetal Heart Ratec (Frequência Cardíaca Fetal)

ECG Eletrocardiograma

NI-fECG Non Invasive fetal ECG (Eletrocardiografia Fetal Não Invasiva)

fECG Eletrocardiograma Fetal

aECG Eletrocardiograma Abdominal

mECG Eletrocardiograma Materno

FGA Faculdade do Gama da Universidade de Brasília

BPM Batimento Por Minuto

SA Nó Sinoatrial

AV Nó Atrioventricular

VFC Variabilidade da Frequência Cardíaca

CTG Cardiotocografia

AES Abdominal Electrode-Sourced (fonte de Eletrodo Abdominal)

CS Combined Source (Fonte Combinada)

RNAs Redes Neurais Artificiais

CNN Convolutional Neural Network (Rede Neural Convolucional)

RELU Rectified Linear Unit (Unidade Linear Retificadora)

FPGA Field-Programmable Gate Array

CLB Configurable Logic Block (Bloco Lógico Configurável)

LUTs Look-Up Tables

IOB In/Out Block(Bloco de entrada e saída)

SB Switch Box (Bloco de seletoras)

BRAM Block Random Access Memory (Bloco de Memória de acesso Aleatório)

DSP Digital Signal Process (Processador de Sinal Digital)

HDL Hardware Description Language (Linguagem de Descrição de Hard-

ware)

VHDL VHSIC Hardware Description Language (VHSIC Linguagem de Des-

crição de Hardware)

ASIC Application Specific Integrated Circuits (Circuitos Integrados de Apli-

cação Específica)

CPU Central Process Unit (Unidade de Processamento Central)

SoC System on a Chip (Sistema em um chip)

ARM Advanced RISC Machine

ASSP Application-specific standard parts (Circuitos integrados para uma apli-

cação específica padrão)

ADALINE Adaptative Linear Netwok

TDL Tapped Delay Line

IP Intellectual Property (Blocos de Propriedade Intelectual)

MatLab  $MATrix\ LABoratory$

XSDK Xilinx Software Development Kit

IDE Integrated Development Environment

USB Universal Serial Bus

VGA Video Graphics Array

LEDs Light-Emitting Diodes

PLL Phase Lock Loop (Bloqueio de fase em loop)

xADC Conversor analógico-digital on-chip

RTL Register Transfer Level

SIPO Single Input Parallel Output

ns Nanossegundos

## Lista de símbolos

$\Gamma$  Letra grega Gama

$\Lambda \qquad \qquad Lambda$

$\in$  Pertence

## Sumário

| 1     | INTRODUÇÃO 21                                         |

|-------|-------------------------------------------------------|

| 1.1   | Contextualização                                      |

| 1.2   | Definição do Problema                                 |

| 1.3   | Objetivos                                             |

| 1.3.1 | Objetivos Gerais                                      |

| 1.3.2 | Objetivos Específicos                                 |

| 1.4   | Estrutura do Trabalho                                 |

| 2     | FUNDAMENTAÇÃO TEÓRICA 25                              |

| 2.1   | ECG Fetal                                             |

| 2.1.1 | Formação e Atividade Cardíaca                         |

| 2.1.2 | Estimativa da FHR                                     |

| 2.2   | Redes Neurais Artificiais                             |

| 2.2.1 | Definição                                             |

| 2.2.2 | Redes Neurais Convolucionais                          |

| 2.2.3 | Treinamento por Backpropagation                       |

| 2.3   | FPGAs                                                 |

| 2.3.1 | Aceleração de Algoritmos                              |

| 2.3.2 | SoCs                                                  |

| 2.4   | Estado da Arte                                        |

| 3     | ASPECTOS METODOLÓGICOS                                |

| 3.1   | Metodologia                                           |

| 3.2   | Ferramentas                                           |

| 3.2.1 | MatLab                                                |

| 3.2.2 | Vivado                                                |

| 3.2.3 | ILA Core                                              |

| 3.2.4 | XSDK                                                  |

| 3.2.5 | Basys 3 Artix-7                                       |

| 4     | IMPLEMENTAÇÃO DA ARQUITETURA PROPOSTA 45              |

| 4.1   | Sinal aECG gerado no MatLab                           |

| 4.2   | Descrição da arquitetura proposta                     |

| 4.3   | Implementação da CNN em C no ARM                      |

| 4.4   | Descrição da Primeira Camada Convolucional em VHDL 48 |

| 4.4.1 | Componente do <i>loop</i> interno                     |

| 4.4.2 | Módulo Principal                                                                                |

|-------|-------------------------------------------------------------------------------------------------|

| 4.5   | Implementação do projeto em Hardware com o ILA 53                                               |

| 5     | RESULTADOS E DISCUSSÕES 55                                                                      |

| 5.1   | Análise de <i>Profiling</i>                                                                     |

| 5.2   | Simulações Comportamentais                                                                      |

| 5.2.1 | Testbench do componente do loop interno                                                         |

| 5.2.2 | Testbench do módulo principal                                                                   |

| 5.3   | Testes de implementação em hardware com o ILA Core 58                                           |

| 5.4   | Análise de recursos, energia e timing 61                                                        |

| 5.5   | Hardware vs Software                                                                            |

| 6     | CONCLUSÃO                                                                                       |

| 6.1   | Trabalhos futuros                                                                               |

|       | REFERÊNCIAS 67                                                                                  |

|       | APÊNDICES 71                                                                                    |

|       | APÊNDICE A – CÓDIGO VHDL DA BIBLIOTECA FPUPACK 73                                               |

|       | APÊNDICE B – CÓDIGO VHDL QUE DESCREVE O LOOP IN-<br>TERNO DA PRIMEIRA CAMADA CONVOLU-<br>CIONAL |

|       | APÊNDICE C – CÓDIGO VHDL DO MÓDULO PRINCIPAL DA CAMADA CONVOLUCIONAL COM FSM 83                 |

|       | APÊNDICE D – CÓDIGO VHDL DO MÓDULO QUE INSTAN-<br>CIA O II A PARA TESTES EM HARDWARE 91         |

## 1 Introdução

## 1.1 Contextualização

A frequência cardíaca fetal (FHR - Fetal Heart Rate) é o intervalo entre as batidas consecutivas do coração fetal em desenvolvimento por unidade de tempo, ou seja, representa o batimento cardíaco e a atividade do coração. Ele fornece informações para determinar as condições de saúde do feto o que ajuda no prognóstico gestacional. De acordo com (SAKURAI; LIMA; FARIA, 2001), a curva de normalidade para a FHR entre a  $10^{\rm a}$  e a  $14^{\rm a}$  semana de gestação é entre 136 e 178 BPM, havendo diminuição progressiva e significativa da FHR com o avanço da idade gestacional.

Em 1953, surgiu o primeiro método para monitorar continuamente a FHR por meio da eletrocardiografia fetal não invasiva (NI-fECG). Em paralelo, surgiu a cardiotocografia fetal ultrassônica, outro método não invasivo para monitoramento da FHR e das contrações uterinas. Já em relação aos métodos invasivos, tem-se o método de monitoramento fetal eletrônico interno, onde a FHR é determinada de forma mais precisa usando sinais medidos por um eletrodo de couro cabeludo fetal (KAHANKOVA et al., 2020).

O NI-fECG permanece como o método alternativo mais promissor para monitoramento fetal contínuo, pois a partir dele é possível obter informações fisiológicas únicas para identificar sofrimento fetal incapazes de serem obtidos pelo método de cardiotocografia, devido à natureza de suas medições. Além de ser um método não invasivo, em que não há exposição da mãe e do feto a radiação, o sinal do fECG (Eletrocardiograma Fetal) carrega informações valiosas, como estados patológicos (isquemia miocárdica, hipóxia intraparto ou acidose metabólica) que são identificadas como alterações na morfologia da forma de onda de fECG (segmento ST, intervalo QT). A partir do fECG também é possível estabelecer diagnósticos para má formação do coração e bradicardia (KAHANKOVA et al., 2020).

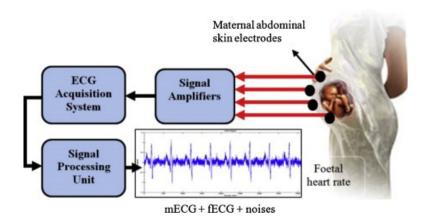

Sendo assim, o método do NI-fECG foi o mais adequado para abordagem de monitoramento do FHR do presente projeto. O seu sistema de aquisição, consiste em posicionar os eletrodos no abdômen materno e o sinal resultante coletado é o eletrocardiograma abdominal (aECG), que é composto pelo eletrocardiograma materno (mECG), pelo fECG e por ruídos diversos, como por exemplo das contrações uterinas. A partir do processamento do aECG, pode-se extrair o fECG e aplicar algoritmos de estimação para se obter a FHR (JAGANNATH; SELVAKUMAR, 2014).

A figura 1 apresenta o sistema de aquisição do aECG, junto ao processo de extração do fECG.

Figura 1 – Sistema de aquisição aECG e extração do fECG para estimativa do FHR. FONTE: (JAGANNATH; SELVAKUMAR, 2014)

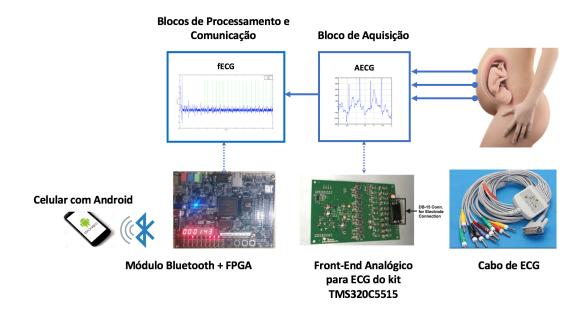

Está sendo desenvolvido na Faculdade do Gama da Universidade de Brasília (FGA), um protótipo para estimar a FHR a partir do fECG utilizando um dispositivo reconfigurável, com co-projeto hardware-software, para a implementação e aceleração dos algoritmos de processamento de sinais. O sistema completo, vide Figura 2, é composto por 3 blocos:

- Aquisição: neste bloco serão coletadas as amostras de aECG. Será utilizada uma placa de front-end analógico para ECG do Medical Development Kit TMS320VC5505 da Texas Instruments, que efetuará a leitura dos sensores de ECG (eletrocardiograma) posicionados no abdômen da gestante e enviará os sinais amostrados para o bloco de processamento. Atualmente, o sistema de aquisição está configurado somente para escrever os dados em um cartão de memória (TUTIDA, 2016);

- Processamento: este bloco contém um kit com um dispositivo FPGA (Field Programmable Gate Array), no qual um processador softcore embarcado será utilizado para aceleração de algoritmos a partir da exploração das possibilidades de paralelismo oferecidas pela implementação em hardware e software. Até o presente momento, foram implementadas duas abordagens para processar o aECG e realizar a estimativa da FHR: filtro adaptativo (BARBOSA, 2016) e redes neurais (JUNIOR, 2018);

- Comunicação: este bloco também será implementado no mesmo processador softcore

embarcado em FPGA e realizará a comunicação sem fio com um dispositivo móvel.

A implementação realizada até o momento permite realizar a transmissão da FHR

via Bluetooth para um smartphone com sistema Android, que por sua vez contém

um aplicativo que recebe os dados e emite alarmes caso os mesmos ultrapassem os

limites pré-definidos (RODRIGUES, 2016).

O escopo do presente projeto está em implementar um acelerador de hardware em FPGA para o algoritmo da Redes Neural Convolucional, proposta por (JUNIOR, 2018), para o bloco de processamento do protótipo.

Figura 2 – Protótipo de sistema para estimativa da FHR através da aquisição de sinais aECG. Em desenvolvimento pela Universidade de Brasília - FGA.

## 1.2 Definição do Problema

Na arquitetura de rede neural convolucional proposta por (JUNIOR, 2018), foram utilizados sinais simulados de aECG, gerados em MatLab, onde a partir destes sinais a rede foi treinada e testada.

Entretanto, a arquitetura foi descrita apenas na linguagem C e executada em software, não sendo testada em um microprocessador instanciado em hardware devido a limitações de memória do dispositivo utilizado, onde houve a tentativa do uso do processador softcore MIPSfpga no chip FPGA do kit de desenvolvimento Basys3. Além disso, não houve a descrição de nenhuma das camadas da arquitetura da rede neural em VHDL e sua respectiva implementação em hardware em FPGA.

Portanto, o problema a ser resolvido no presente projeto é a aceleração em FPGA das camadas com alto custo computacional da arquitetura da Rede Neural Convolucional proposta.

## 1.3 Objetivos

## 1.3.1 Objetivos Gerais

Implementar em FPGA, a aceleração do algoritmo da Rede Neural Convolucional proposta por (JUNIOR, 2018), para a primeira camada convolucional da arquitetura da rede, haja vista que as camadas convolucionais da rede requerem alto custo computacional, demandando maior tempo de execução quando realizado via software.

### 1.3.2 Objetivos Específicos

Para obter sucesso no objetivo geral do projeto, os seguintes objetivos específicos são necessários:

- Implementação do código da arquitetura da Rede Neural Convolucional no ARM;

- Descrição em VHDL do código para a primeira camada convolucional da rede e realizando testes comportamentais;

- Implementação em hardware da primeira camada convolucional com teste usando o ILA core;

### 1.4 Estrutura do Trabalho

O presente trabalho está composto de 6 capítulos. No Capítulo 1, tem-se a Introdução, onde são apresentados a contextualização e objetivos do trabalho. No Capítulo 2, é abordada a fundamentação teórica, explicitando conceitos bases para a compreensão do projeto, como o desenvolvimento cardíaco de um feto, o que são Redes Neurais Artificiais, o que é FPGA, SoC e sua aplicação em aceleração de algoritmos e, por fim, uma apresentação de trabalhos correlatos. No Capítulo 3, é mostrada a metodologia do projeto, como também as ferramentas utilizadas para o desenvolvimento do mesmo. O Capítulo 4 apresenta a implementação da primeira camada convolucional que foi proposta na arquitetura da Rede Neural, por meio de esquemáticos e diagramas que mostram como foi descrito o bloco de circuito. No Capítulo 5 são apresentados os resultados obtidos e discussões a respeito da implementação em FPGA da primeira camada convolucional descrita em VHDL, trazendo a comparação de desempenho entre hardware e software, dentre outros parâmetros de análise. Por fim, no Capítulo 6 tem-se a conclusão do projeto, onde é comentado os sucessos e fracassos para os objetivos propostos e sugestões para trabalhos futuros.

## 2 Fundamentação Teórica

### 2.1 ECG Fetal

### 2.1.1 Formação e Atividade Cardíaca

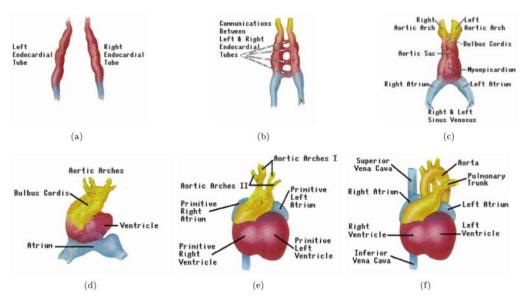

O coração está entre os primeiros órgãos desenvolvidos na formação do feto, onde nos primeiros estágios da gravidez, sofre um crescimento considerável. O período mais crítico desse desenvolvimento é entre a 3ª e 7ª semana, quando um tubo cardíaco simples assume a forma de um coração de quatro câmaras (SAMENI; CLIFFORD, 2011).

A partir da 3ª semana de vida, o coração já começa a bater e realizar a circulação de seu próprio sangue, em um sistema circulatório fechado e separado do da mãe. A figura 3 apresenta os estágios de desenvolvimento do coração fetal durante a gestação em ordem cronológica.

Figura 3 – Estágios de desenvolvimento do coração fetal de (a) a (f): a)tubos endocárdicos. b)comunicações entre tubos endocárdicos. c) arcos aórticos, sacos aórticos, mioepicárdio, átrios e seios venosos d)arcos aórticos, bulbus cordis, ventríloco e átrio e)arcos aórticos I, arcos aórticos II, átrios primitivos, ventrílocos primitivos f)veia cava superior, aorta, tronco pulmonar, átrios, ventrílocos, veia cava inferior. FONTE: (SAMENI; CLIFFORD, 2011)

Por volta da 7ª a 9ª semana, o coração fetal pode ser monitorado externamente por meio de ultrassom. Na 20ª semana, é possível escutar o batimento cardíaco fetal sem amplificação, com uma taxa entre 120-160 BPM (Batimento Por Minuto), aproximadamente. Todavia, poucas informações adicionais de diagnóstico podem ser determinadas a partir da escuta da frequência cardíaca neste período. Surge então, a necessidade do

uso de equipamentos como o Eletrocardiógrafo para análises do fECG (Eletrocardiograma Fetal) e do mECG (Eletrocardiograma Materno), que contêm informações morfológicas da atividade cardíaca que são interessantes para análises clínicas (SAMENI; CLIFFORD, 2011).

Embora a função mecânica do coração fetal seja diferente da de um coração adulto, sua atividade elétrica pulsante é bastante semelhante. A ação de bombeamento em forma de onda do coração é realizada no miocárdio a partir de contrações e relaxamentos regulares. A estimulação miocárdica inicia no nó sinoatrial (SA), que funciona como o marca-passo natural do coração, enviando o impulso elétrico que dispara cada batimento cardíaco. Esse impulso estimula ainda o nó atrioventricular (AV) e posteriormente ocorre a despolarização dos músculos ventriculares. A etapa de contração do miocárdio é chamada de ciclo de despolarização que é seguido pelo ciclo de repolarização, no qual o miocárdio relaxa e fica pronto para a próxima ativação. (SAMENI; CLIFFORD, 2011).

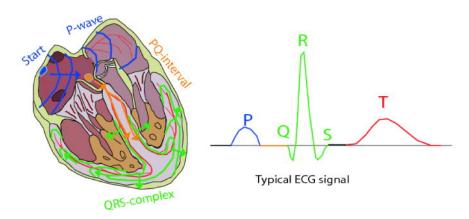

O ECG medido na superfície corporal é o resultado da ativação em estágio do miocárdio e resulta no complexo PQRST, ciclo cardíaco completo representado na Figura 4. Nesta notação, a onda P é responsável pela propagação da frente de despolarização através dos átrios. Em seguida, os ventrículos são despolarizados resultando no complexo QRS. Ao mesmo tempo, os átrios são repolarizados; no entanto, essa repolarização é obscurecida pela despolarização dos ventrículos. Por fim, temos a onda T, que corresponde à repolarização dos ventrículos.

Figura 4 – O ciclo de ativação do coração fetal. FONTE: (SAMENI; CLIFFORD, 2011)

#### 2.1.2 Estimativa da FHR

Morfologicamente, adultos e fetos apresentam padrões de ECG bastante semelhantes; mas as amplitudes relativas dos complexos fetais sofrem mudanças consideráveis ao longo da gestação e mesmo após o nascimento. A mudança mais considerável diz respeito às ondas T, que são bastante fracas para fetos e recém-nascidos. A partir da 20<sup>a</sup> semana, a FHR (Fetal Heart Rate - Frequência Cardíaca Fetal) tem um valor basal de cerca de

2.1. ECG Fetal 27

120 a 160 batimentos por minuto (BPM). No entanto, embora as variações da frequência cardíaca fetal sejam diferentes para crianças e adultos, a FHR é conhecida por possuir variações circadianas que evoluem ao longo da gravidez. Estruturalmente, a variabilidade da frequência cardíaca (VFC) do feto também é conhecida por ser mais simples (menos variante) do que a de um adulto (SAMENI; CLIFFORD, 2011).

A medida da FHR é de extrema importância para o prognóstico gestacional. É necessário observar sempre se a mesma está dentro dos limites de normalidade conforme a idade gestacional, visto que contribui para a suspeita de anomalia cromossômica fetal, predição do risco para anomalias cromossômicas, diagnóstico para presença de infecção concomitante, prevenção de perda gestacional, etc (SILVA; BAILãO, 2000).

O método mais promissor para monitoramento fetal é a Eletrocardiografia fetal não invasiva (NI-fECG). O principal motivo para essa afirmação é que o sinal de fECG não podem ser obtidos a partir de um monitoramento de cardiotocografia (CTG), devido à natureza de suas medições. Além disso, no método NI-fECG não há a exposição a nenhum tipo de radiação para a mãe e o feto. As contrações uterinas podem ser monitoradas pela detecção da atividade elétrica no abdômen materno (KAHANKOVA et al., 2020).

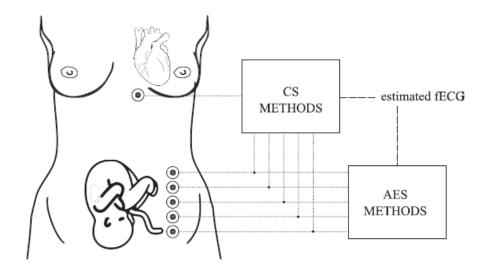

Para os algoritmos de extração do fECG, há duas categorias em relação a medição dos sinais: algoritmos que requerem apenas eletrodos abdominais, chamados métodos com fonte de eletrodo abdominal (*Abdominal Electrode-Sourced* - AES), e algoritmos que requerem eletrodos abdominais e torácicos, chamados métodos de fonte combinada (*Combined Source* - CS). Os princípios dessa categorização são ilustrados na Figura 5.

Figura 5 – Ilustração dos sistemas de extração AES e CS. FONTE: (KAHANKOVA et al., 2020)

Dentre as técnicas de processamento para o AES podemos destacar os filtros de Kalman e as transfomadas Wavelet. Por outro lado, no método CS, tem-se os Filtros de Mínimos Quadrados Médios e Mínimos Quadrados Recursivos, assim como a aplicação

de RNAs. Entre várias possibilidades, o método mais eficiente para extração de fECG consiste na combinação de diferentes técnicas e na criação de sistemas híbridos, que se mostram mais promissores na finalidade de alcançar uma estimativa precisa da frequência cardíaca fetal (KAHANKOVA et al., 2020).

#### 2.2 Redes Neurais Artificiais

### 2.2.1 Definição

As Redes Neurais Artificiais (RNAs) são máquinas computacionais de estrutura conexionista que têm como objetivo aproximar, generalizar, adaptar-se e gerar informações baseadas na experiência para execução de uma tarefa ou função. Seu sistema de processamento não-algorítmico é distribuído por um grande número de pequenas unidades interligadas que em algum nível lembram a estrutura do cérebro (FILHO, 2018).

De acordo com (HAYKIN, 2001):

Uma rede neural é um processador maciçamente paralelamente distribuído constituído de unidades de processamento simples, que têm a propensão natural para armazenar conhecimento experimental e torná-lo disponível para o uso. Ela se assemelha ao cérebro em dois aspectos:

- 1. O conhecimento é adquirido pela rede a partir de seu ambiente através de um processo de aprendizagem.

- 2. Forças de conexão entre neurônios, conhecidas como pesos sinápticos, são utilizadas para armazenar o conhecimento adquirido.

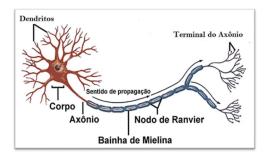

Os neurônios biológicos, por sua vez, são células presentes no sistema nervoso que possuem como principal função conduzir os impulsos nervosos e constituem-se de partes básicas. São elas: o corpo celular, os dendritos e o axônio (BEAR, 2008), formando a seguinte estrutura apresentada na figura 6. De forma semelhante, o neurônio artificial tenta aproximar-se do modelo biológico em estrutura e funcionalidade.

Figura 6 – Composição de um neurônio biológico. FONTE: (BRITO, 2019)

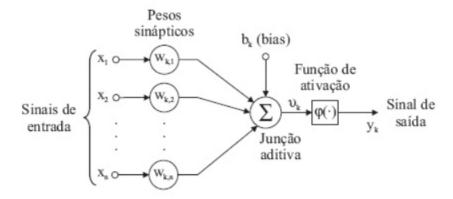

De acordo com (BRAGA, 2000) dentre os diferentes componentes que um modelo básico de RNA possui, temos:

- Conjunto de sinapses: conexões entre os neurônios da RNA, por onde entram os sinais. Para cada conexão é atribuído um peso sináptico;

- Junção aditiva: realiza as somas dos sinais de entrada da RNA, ponderados pelos pesos sinápticos;

- Bias: valor externo acrescido a cada neurônio com o objetivo de aumentar ou diminuir a entrada líquida da função de ativação.

- Função de ativação: função que limita a amplitude do valor do sinal de saída de um neurônio;

Na figura 7, tem-se a estrutura de um neurônio artificial de modelo não linear. Os sinais de entradas  $x_k$  são multiplicados pelos pesos sinápticos  $w_{kj}$  e somados entre si na função aditiva  $u_k$ , acrescidos por um bias  $b_k$ . Por fim, o resultado do somatório passa pela função de ativação  $\varphi$ , resultando no sinal de saída  $y_k$ .

Figura 7 – Modelo não linear de um neurônio. FONTE: (HAYKIN, 2001)

As equações 2.1 e 2.2 fornecem o modelo matemático para o neurônio artificial:

$$u_k = \sum_{j=1}^m w_{kj} x_j \tag{2.1}$$

$$y_k = \varphi(u_k + b_k) \tag{2.2}$$

#### 2.2.2 Redes Neurais Convolucionais

A Rede Neural Convolucional (ou *Convolutional Neural Network* - CNN) é uma arquitetura derivada do modelo de rede Perceptron de Múltiplas Camadas, sendo ampla-

mente aplicada no campo de visão computacional para dados visuais. A concepção da CNN consiste em múltiplas camadas com diferentes funcionalidades, onde os neurônios das camadas são responsáveis pela aplicação de filtros, cada um (VARGAS; CARVALHO; VASCONCELOS, 2016).

As RNAs são arquiteturas treináveis compostas de múltiplos estágios. A entrada e a saída de cada estágio são conjuntos de matrizes chamados feature maps (mapas de características). Na saída, cada feature map representa um recurso específico extraído em todos os locais da entrada. Cada estágio é composto de três camadas: uma camada de banco de filtros, onde é aplicada a convolução da entrada e é feito o acréscimo do bias treinado, uma camada de não linearidade e uma camada de pooling onde ocorre um agrupamento das características. Uma CNN típica é composta por um, dois ou três desses estágios de 3 camadas, seguidos por um módulo de classificação (LECUN; KAVUKCUO-GLU; FARABET, 2010).

A figura 8 mostra um modelo de CNN e a disposição das camadas, que são: camada de convolução, camada de não linearidade, camada de pooling, camada flatten, camada densa (fully-connected) e camada de saída.

Figura 8 – Modelo de uma rede neural convolucional e suas diferentes camadas. FONTE: (VARGAS; CARVALHO; VASCONCELOS, 2016)

- Camada de convolução Segundo (KHAN et al., 2018) esta é a camada mais importante da CNN, pois nela ocorre a convolução da entrada com um conjunto de filtros chamados kernels, gerando o mapa de características.

- Camada de não linearidade Considerada por alguns autores como a função de ativação do neurônio da camada convolucional, sua função é amenizar os efeitos da linearidade em redes neurais, onde a maioria dos problemas são não lineares. Atualmente utiliza-se a função ReLU (Rectified Linear Unit) para a maioria das aplicações.

- Camada de pooling nesta camada temos um processo simples de downsampling, onde a dimensionalidade/feature maps é reduzida. A variância da informação a pequenas alterações é reduzida, assim como a quantidade de parâmetros treinados pela rede.

- Camada flatten É responsável por operar uma transformação na matriz da fornecida pela camada anterior, alterando seu formato para um vetor. Basicamente, os dados são alinhados e concatenados de forma que a camada densa possa lê-los corretamente.

- Camada densa Trata-se de uma RNA simples, que recebe os dados tratados pelas camadas anteriores e, a partir deles, generaliza e realiza a classificação dos dados para a camada de saída.

### 2.2.3 Treinamento por Backpropagation

O algoritmo de retropropagação de erro, referido na literatura como *Backpropagation*, é um processo de treinamento supervisionado para RNAs baseado na regra de aprendizagem por correção de erro. Consiste de dois passos realizados dentro das camadas da rede: a propagação e a retropropagação. Na propagação, vetores de entrada são aplicados aos nós da rede, propagando o seu efeito, camada por camada, produzindo um conjunto de saídas como a resposta real da rede. Durante este passo, os pesos sinápticos são todos estáticos. Já na retropropagação, todos os pesos sinápticos são ajustados conforme uma regra de correção de erro e a resposta real da rede é subtraída do valor esperado, produzindo um sinal de erro que é propagado para trás pela rede, contrário aos pesos sinápticos. Por fim, o procedimento é realizado repetidamente, sempre ajustando os pesos sinápticos para fazer com que a resposta real da rede aproxime o máximo do valor esperado, estatisticamente (HAYKIN, 2001).

A Figura 9, apresenta um diagrama esquemático básico do algoritmo de treinamento de retropropagação, onde ao obter a saída da rede neural, calcula-se o erro pela diferença entre o resultado de saída ("Obs") e o resultado esperado ("Model"), avaliando se este erro é tolerável ou não. Caso o erro não esteja satisfazendo a tolerância, ocorre a retropropagação do erro no sentido contrário nas camadas da rede neural, onde são calculados os valores dos gradientes para cada peso da rede tomando o sentido contrário dele, na tentativa de minimizar o valor da função de erro. Uma vez que tem-se o vetor gradiente calculado, os pesos são atualizados no sentido de modo iterativo, sempre recalculando os gradientes em cada passo de iteração, até que o erro diminua e alcance um valor menor que a tolerância estabelecida, finalizando assim o algoritmo de treinamento.

O desenvolvimento do algoritmo de retropropagação representou um marco nos conceitos de aprendizagem das redes neurais, que embora não forneça uma solução perfeita

Figura 9 – Diagrama esquemático do algoritmo de treinamento de retropropagação e modelo de neurônio típico. FONTE: (KIM; SEO, 2015)

para os problemas solúveis, fornece um método computacional eficiente para o treinamento das RNAs, em especial as redes perceptrons de múltiplas camadas (HAYKIN, 2001).

### 2.3 FPGAs

FPGA (Field-Programmable Gate Array) é um dispositivo lógico programável que possui uma arquitetura baseada em blocos lógicos configuráveis alocados em forma de uma matriz. Em geral, a funcionalidade e o roteamento destes blocos são configuráveis, e as vezes reconfiguráveis, via software. Os FPGAs proporcionam um ambiente de trabalho simplificado e de baixo custo, possibilitando operar com um número ilimitado de circuitos por meio da configuração do próprio dispositivo (ORDONEZ, 2003).

A arquitetura básica de um FPGA é mostrada na Figura 10. Esta pode variar de acordo com a fabricante do dispositivo, com as categorias ou até em uma mesma categoria podem existir variações, que dependem da sua área de aplicação. Todavia, podemos destacar os principais elementos que compõe um FPGA:

- CLB (*Configurable Logic Block*): são as unidades lógicas de uma FPGA, formados por *flip-flops* e *look-up tables* (LUTs).

- IOB (*In/Out Block*): bloco dos periféricos de entrada e saída do FPGA, localizado na periferia dos FPGAs, sendo responsáveis pela interface com o ambiente.

- SB (Switch Box): são as interconexões programáveis entre os CLBs, através dos canais de roteamento.

2.3. FPGAs 33

• BRAM (*Block Random Access Memory*): é o bloco de memória intrínseco ao chip, não presente em todos FPGAs. Dentro da limitação do tamanho do BRAM, as células de memória interna podem ser subdivididas e cascateadas para formarem blocos conforme necessidade de armazenamento configurado no projeto.

• DSP (*Digital Signal Process*): são unidades especializados em processamento digital de sinal, também não presente em todos FPGAs. Estes blocos são dedicados para processar funções como filtragem, multiplicação, conversão analógico-digital e vice versa, etc. São consideravelmente mais eficientes quando comparados aos CLBs.

Figura 10 – Arquitetura interna de um chip FPGA típico. FONTE: (BAJAJ; FAHMY, 2015)

A chamada Hardware Description Language (HDL), é a linguagem utilizada programar os circuitos lógicos eletrônicos dentro dos FPGAs, que descreve as estruturas, operação e projeto dos circuitos nos dispositivos. A linguagem HDL possui uma sintaxe composta de operadores, expressões, estruturas e operações de entrada e saída. Ao contrário das linguagens de programação de software, que geram um assembly executável no computador, a HDL provê um mapa de portas, algumas vezes mencionados como bitstream. O bitstream obtido é carregado no dispositivo FPGA com objetivo de verificar sua operação. A linguagem permite descrever qualquer circuito digital de forma estrutural e comportamental (BERBERT; BERTINI; COPETTI, 2021).

### 2.3.1 Aceleração de Algoritmos

Devido às características de flexibilidade, confiabilidade e paralelismo fornecidas pelos FPGAs, destaca-se a possibilidade de utilizar esses recursos para executar tarefas específicas de alto desempenho em que é necessário o máximo de eficiência, tanto em poder computacional quanto em velocidade na execução, como por exemplo o processamento de dados em tempo real. Com o FPGA, é possível ajustar os recursos de hardware em tempo de execução de modo a atender as mudanças de requisitos de energia, desempenho e tolerância a falhas (BERBERT; BERTINI; COPETTI, 2021).

A principal vantagem dos sistemas com processadores FPGA é a flexibilidade. Todavia, quando a premissa de um projeto é o desempenho, os sistemas ASIC (*Application Specific Integrated Circuits*) são preferíveis em sacrifício à flexibilidade. Já quando o desempenho é necessário, mas não é possível deixar a flexibilidade completamente de lado, uma solução comum é a implementação dos sistemas híbridos, onde os processadores em ASIC são associados com partes em FPGA, combinando desempenho e eficiência e mantendo parte da flexibilidade (BERBERT; BERTINI; COPETTI, 2021).

Aceleração de hardware é a técnica do uso de uma arquitetura feita exclusivamente para realizar uma tarefa específica que executa as operações de forma mais eficiente do que se a mesma fosse feita utilizando um software para uma CPU (Central Process Unit) de uso geral. A aceleração de hardware implementada em FPGA tem sido bastante aplicada e com sucesso na aceleração de algoritmos como por exemplo na área de Deep Learning, em particular nas CNNs em aplicações de reconhecimento de imagens relacionados à Visão Computacional (BERBERT; BERTINI; COPETTI, 2021).

#### 2.3.2 SoCs

O SoC (System on a Chip) é um circuito integrado no qual pode-se ter um sistema eletrônico ou de computador completo, com processador, memória, arquitetura de cone-xão, etc. Adicionando a lógica programável do FPGA, tem-se então a possibilidade de realizar modificações na estrutura de hardware. Sendo possível adicionar novos módulos ao SoC, aqueles podem acelerar e auxiliar os processadores embarcados em tratamentos que requerem alta capacidade de processamento. A comunicação do sistema de processamento com o sistema programável é feita através de um barramento interno, estabelecendo a integração do software com o hardware (CUNHA, 2014).

A utilização de SoCs acrescenta as seguintes vantagens em suas aplicações:

- redução do tempo de projeto;

- redução na quantidade de componentes eletrônicos, diminuindo o custo e aumentando a confiabilidade do sistema;

2.3. FPGAs 35

• aumento no desempenho, uma vez que todos os componentes estão dentro do mesmo circuito integrado;

maior flexibilidade de adaptações e atualizações nos algoritmos descritos em hardware.

A figura 11 mostra um exemplo da arquitetura do Zynq@-7000 SoC, um dispositivo SoC da Xilinx que integra a programabilidade do software de um processador baseado em ARM(Advanced RISC Machine) com a programação do hardware de um FPGA, permitindo análises importantes e aceleração de hardware enquanto integra CPU, DSP, ASSP(Application-specific standard parts) e funcionalidade de sinal misto em um único dispositivo (XILINX, 2021). A região da Lógica Programável representa a parte do FPGA, enquanto o Sistema de Processamento pode ser um processador dedicado ou CPU, por exemplo.

Figura 11 – Diagrama de Blocos estrutural do Zynq-7000 Soc. FONTE:(XILINX, 2021)

#### 2.4 Estado da Arte

Após ampla pesquisa, destacou-se apenas um autor, ou grupo de autores, que difundiu trabalhos específicos para a extração de sinais fECG por meio de redes neurais implementadas em FPGA.

Em uma primeira abordagem, (HASAN; IBRAHIMY; REAZ, 2009) apresentou apenas a arquitetura e algoritmo da extração do fECG através de redes neurais com abordagem de filtros adaptativos que combinam ADALINE (Adaptative Linear Netwok) e TDL (Tapped Delay Line), onde concluiu que a técnica de filtragem de rede neural adaptativa trouxe resultados satisfatórios, mas que a precisão da saída depende de quantas variações de sinais são usadas como entrada e o alvo na rede neural.

Já em (HASAN et al., 2009), foi realizada a modelagem em VHDL (VHSIC Hardware Description Language) do algoritmo desenvolvido em (HASAN; IBRAHIMY; REAZ, 2009) para implementações em FPGAs. O modelo proposto foi sintetizado e inserido no Stratix II EP2S15F484C3 da Altera usando o Quartus II versão 7.2 Web Edition. Os resultados obtidos nas simulações do Quartus II, para o modelo em VHDL, foram similares aos resultados obtidos pelas simulações no MatLab, porém não foi implementado na FPGA.

Em continuidade, em (HASAN; REAZ, 2012), foram abordadas a implementação e a prototipagem do algoritmo em hardware no FPGA, onde foi afirmado que o algoritmo desenvolvido é capaz de extrair completamente o fECG do aECG e que o desempenho obtido para detecção de pico-R no monitoramento da FHR foi de 93,75%, onde relatórios de síntese indicaram que a utilização lógica do FPGA foi de 36%, com 1721 registradores e 56 DSPs usados no total.

Saindo do contexto de extração de fECG, (MAIA, 2020) propôs um sistema automático para geração de arquiteturas SoC para a execução de CNNs em FPGA, por meio da implementação de subsistemas co-design entre software e hardware. Neste projeto foi utilizado a técnica de análise de alto nível, gerando um IP de coprocessador para a camada de convolução da rede. Foram apresentados resultados em que a camada de convolução implementada em hardware obteve tempo de execução 15,2 vezes mais rápido do que a convolução implementada em software.

Um trabalho desenvolvido por (TOMASI, 2020) apresentou um acelerador de hardware em FPGA para aplicações em aprendizado de máquina, por meio da implementação de duas arquiteturas dedicadas para o cálculo da entrada da função de ativação de uma rede neural perceptron. Os resultados mostraram um bom compromisso de design onde a primeira arquitetura obteve tempo de execução de 270ns, enquanto a segunda pode ser computada em 330ns, sendo esta cerca de 4 vezes mais rápida e 50 vezes mais eficiente que um script em Python.

2.4. Estado da Arte

O presente trabalho é oriundo do trabalho desenvolvido por (JUNIOR, 2018), onde foi proposta a arquitetura de Rede Neural Convolucional para estimativa da FHR baseado em FPGA, que em resultados de simulação por software a rede apresentou 96,78% como o menor percentual de acerto registrado e 98,36% como o maior, com um desvio padrão de 0,67% e valor médio igual a 97,43%.

# 3 Aspectos Metodológicos

## 3.1 Metodologia

No que tange à metodologia do projeto, foi utilizada uma abordagem qualitativa para a implementação da CNN no FPGA, com finalidade de analisar os resultados obtidos, desafios encontrados e proposição de soluções e melhorias, para obter então o melhor sistema para se adequar ao projeto de estimativa da FHR pelo fECG.

A fim de compreender o contexto do problema evidenciado, foi realizada uma pesquisa teórica para compreensão da formação cardíaca do feto, início do FHR e seus valores normais, métodos para estimativa do FHR e a sua importância, interpretação do ECG e meios de aquisição dessa informação. Também foi realizada pesquisa teórica a respeito das redes neurais artificiais, abordando os tipos de arquiteturas, as aplicações de cada uma e os principais métodos de implementação, em especial a Rede Neural Convolucional, onde foram destacadas as vantagens, aplicação em visão computacional e o detalhamento funcional, camada por camada.

Com base no entendimento do trabalho desenvolvido por (JUNIOR, 2018), foi estudada a arquitetura proposta da CNN e a sua implementação em linguagem C. Foi reproduzida a geração do sinal sintético de aECG no MatLab para testes na CNN proposta. Então, foram pesquisados os métodos de aceleração de algoritmos e as vantagens de utilização de FPGAs e sistemas SoC.

Foi descrita em VHDL a primeira camada convolucional da CNN proposta, uma vez que as demais camadas convolucionais podem se derivar desta, com alterações nas dimensões dos dados e das iterações. A camada convolucional é a camada que mais exige poder computacional, sendo a mais indicada para aproveitar o paralelismo fornecidos pelos FPGAs.

Por fim, foram realizadas simulações comportamentais e validação da implementação do circuito da primeira camada convulucional da rede em hardware, usando o ILA core na ferramenta Vivado, a fim de validar o seu correto funcionamento, comparando os resultados de desempenho do circuito em hardware com os resultados do modelo da camada executadas em software no ARM.

#### 3.2 Ferramentas

Para o desenvolvimento do projeto, foram utilizadas as ferramentas descritas a seguir.

#### 3.2.1 MatLab

MatLab (*MATrix LABoratory*) é um software interativo de alta performance aplicado para cálculo numérico, onde o elemento básico do cálculo é uma matriz que não exige dimensionamento. O software dispõe um ambiente de área de trabalho ajustado para análise iterativa e processos de projeto com uma linguagem de programação que expressa a matemática de matrizes e matrizes diretamente como é escrita, integrando análises numéricas, cálculos com matrizes, processamentos de sinais e construção de ferramentas gráficas (MATHWORKS, 2005).

O MatLab foi utilizado no presente projeto para a geração do sinal sintético de aECG (mECG + fECG) acrescido de ruídos aleatórios gerados para simular possíveis camadas de gordura, contrações uterinas, etc., buscando tornar o sinal mais próximo do real. Este sinal gerado foi usado para testes da rede neural e também para obtenção das amostras de entrada para a camada da rede neural em software e em hardware.

A ferramenta também foi utilizada para gerar os vetores de testes comportamentais, convertendo os valores de entrada e saída da camada de binário para ponto flutuante e vice-versa, além de ser utilizado para cálculo do erro quadrático médio entre os resultados do software e do hardware.

#### 3.2.2 Vivado

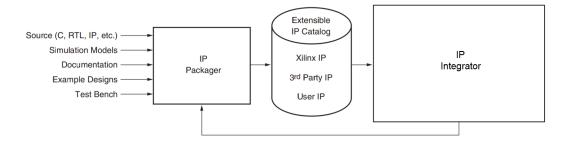

O Vivado Design Suite é um conjunto de software produzido pela Xilinx para síntese e análise de projetos HDL. Substituto do Xilinx ISE, o Vivado possui recursos adicionais para o desenvolvimento de projetos de SoC e síntese de alto nível. O software também simplifica a tarefa de integração de blocos de propriedade intelectual, chamados IP (Intellectual Property) para montar, verificar e implementar e projetos de sistemas que incluem portifólios destes IPs, seja da Xilinx, de terceiros ou próprio (FEIST, 2012).

A integração destes IPs pelo Vivado dentro de um projeto segue o flow mostrado na Figura 12, onde tem se que o IP Package do Vivado permite que a Xilinx, designers e provedores de IP terceirizados empacotem um projeto com suas restrições, bancos de teste e documentação para torná-lo disponível em um catálogo IP extensível em uma unidade local ou compartilhada. Uma vez catalogado, a integração deste amplo portfólio de IP em projetos verificados no nível do sistema pode ser realizada abstratamente no nível da interface usando o integrador Vivado IP com verificação de regras de projeto.

O software Vivado foi utilizado no projeto para a descrição dos códigos em VHDL, instanciação de IPs, testes comportamentais, síntese e implementação do circuito, além de testes em hardware utilizando o ILA core.

3.2. Ferramentas 41

Figura 12 – Vivado Design Suite IP Flow. FONTE: Adaptado de (FEIST, 2012)

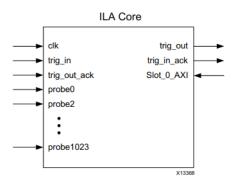

#### 3.2.3 ILA Core

O ILA IP core (*Integrated Logic Analyzer*), é um analisador lógico customizável que pode ser usado para monitorar os sinais internos de qualquer aplicação que exija verificação ou depuração usando o analisador lógico Vivado. Seu núcleo inclui diversos recursos avançados de análise lógica moderna, incluindo como *triggers* as equações booleanas e transições de borda. O monitoramento do ILA é síncronizado com o circuido a ser monitorado, odne todos as restrições de *clock* aplicadas ao projeto também são aplicados aos componentes do ILA. A figura 13 mostra a simbologia do componente do IP ILA core, mostrando entradas de *clock*, os *triggers* e pontas de provas de entrada e saída.

Figura 13 – Símbolo do ILA Core. FONTE:(XILINX, 2016)

O ILA Core foi instanciado e utilizado no projeto para validação do correto funcionamento da primeira camada convolucional descrita em hardware no FPGA.

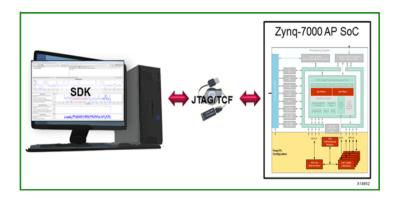

#### 3.2.4 XSDK

O XSDK (Xilinx Software Development Kit) é o IDE (Integrated Development Environment) da Xilinx que permite a aplicação de projetos multiprocessador inteiramente homogêneos e heterogêneos, com depuração e análise de desempenho. Possui um ambiente de projeto integrado para a criação de aplicativos incorporados em qualquer um dos microprocessadores da Xilinx: Zynq@ UltraScale + MPSoC, Zynq-7000 SoCs e o micro-

processador soft-core MicroBlaze. o XSDK é baseado no padrão de código aberto Eclipse (XILINX, 2019).

O software XSDK foi proposto para o desenvolvimento do processador embarcado, onde ocorreria a comunicação do bloco da camada convolucional, descrito em hardware, com o algoritmo da rede neural, descrito em software. A Figura 14 exemplifica um diagrama de comunicação com a utilização do xSDK.

Figura 14 – comunicação Host-Target para o xSDK. FONTE:(XILINX, 2019)

O XSDK foi utilizado para executar a análise de *profile* da rede neural em C no ARM instanciado em IP core e implementado no SoC Zynq-7000 da placa de desenvolvimento Zybo do laboratório remoto da FGA/UnB.

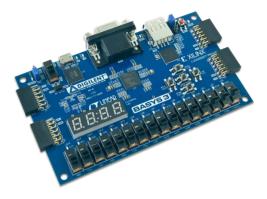

### 3.2.5 Basys 3 Artix-7

Para implementação do projeto no FPGA, foi utilizado o kit Basys 3 (vide figura 15), que é uma plataforma completa de desenvolvimento de circuito digital e pronta para uso baseada no mais recente Artix-7 FPGA da Xilinx. O seu FPGA, o Artix-7, é de baixo custo, possui alta capacidade e uma série de portas USB, VGA e outras. O Basys 3 permite implementar projetos de circuitos combinacionais simples e também circuitos sequenciais complexos que usam processadores e controladores incorporados, além de possuir *switches*, LEDs e pinos I/O, o que faz esse kit ser amplamente utilizado no aprendizado e introdução do mundo dos FPGAs (DIGILENT, 2016).

O FPGA Artix-7 é otimizado para lógica de alto desempenho e oferece alta capacidade, desempenho e uma gama de recursos para o projetista. Os recursos do Artix-7 incluem:

- 33.280 células lógicas em 5200 blocos (cada bloco contém quatro LUTs de 6 entradas e 8 flip-flops);

- 1.800 Kbits de BRAM;

3.2. Ferramentas 43

• 5 blocos de gerenciamento de *clock*, cada um com um PLL (*Phase Lock Loop* - bloqueio de fase em loop);

- 90 blocos DSP;

- Clock interno com velocidades de até 450 MHz;

- Conversor analógico-digital on-chip (xADC);

Figura 15 – Basys 3 Artix-7 FPGA. FONTE:(DIGILENT, 2016)

# 4 Implementação da Arquitetura Proposta

## 4.1 Sinal aECG gerado no MatLab

As ondas utilizadas nos testes da arquitetura foram geradas no software MatLab, por meio da função ecg(). Esta função recebe o parâmetro L, que indica o comprimento do ciclo do sinal gerado. Após a função ecg(), foi inserida a função ecg(sgolayfilt()) para suavizar a onda gerada. Por fim, o ciclo de ECG foi repetido algumas vezes para obter um sinal periódico. Para tal, foi definido que a frequência de amostragem desejada é 1 KHz e o tempo de amostragem é de 10 segundos, resultando em um sinal com 10000 pontos, conforme realizado em (JUNIOR, 2018).

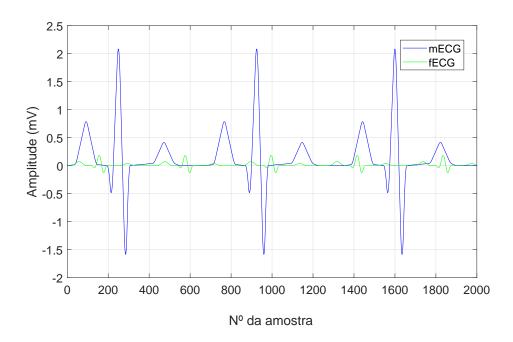

Para gerar o sinal ECG torácico materno, foi definido L=675. Tendo 10000/675 ciclos em 10 segundos, chega-se à frequência de 88.8 BPM. Analogamente, para obter o sinal fECG, foi utilizado L=420 para a função ecg(), resultando em um sinal com FHR de 142.8 BPM. A figura 16 mostra a comparação entre o sinal materno e fetal, onde é possível perceber como o sinal materno possui amplitude muito maior. Observa-se que ambos sinais ainda não possuem ruídos.

Figura 16 – Sinais mECG e fECG sem ruído. Fonte: Autor.

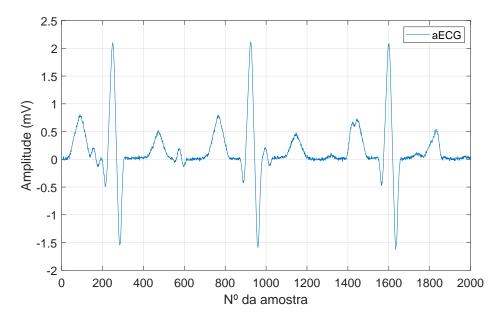

Por fim, para obter a fiel representação de um sinal aECG real, foram somados os sinais mECG e fECG e adicionados ruídos gaussianos brancos e ruídos com coeficientes aleatórios ao sinais, que tentam representar os mais diversos ruídos possíveis, como a

propagação da onda pelos tecidos do corpo, contrações uterinas, etc. O sinal aECG final está mostrado na Figura 17.

Figura 17 – Sinal aECG final gerado no MatlLab. Fonte: Autor.

## 4.2 Descrição da arquitetura proposta

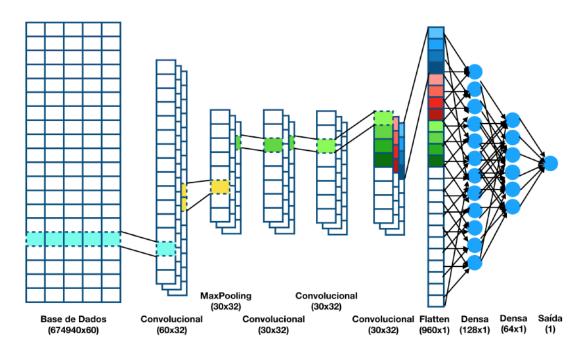

A arquitetura da CNN proposta por (JUNIOR, 2018) é composta de 9 camadas de processamento, cada uma com certa finalidade de extração de dados, redimensionamento ou classificação (vide Figura 18). O conjunto de entrada da CNN é um bloco de dados do sinal ECG com 60 amostras.

A primeira camada convolucional recebe o conjunto das 60 amostras e realiza um ajuste de tamanho, acrescentando 3 amostras nulas no inicio e ao fim do sinal, tornando o conjunto de entrada do sinal com 66 amostras. Esse ajuste na borda do sinal é necessário para que a convolução seja realizada de 7 em 7 amostras do conjunto de 66 amostras. Após o ajuste do sinal é iniciada a convolução da entrada com 32 filtros de tamanho 7x1, onde a saída da camada resulta em uma matriz de dados tamanho 60x32 que refletem a extração de características que sejam significativas na amostra.

A segunda camada, de *maxpooling*, realiza o agrupamento das amostras de 2 a 2 na matriz, retirando a amostra de menor valor. Dessa forma, tem-se o realce das características que foram extraídas na camada anterior. O dado resultante dessa camada é uma matriz de tamanho reduzido pela metade (para 30x32).

A terceira, quarta e quinta camada são convolucionais e têm como função realçar ainda mais as características mais relevantes do conjunto de amostras. O que altera de uma camada para outra são as dimensões dos filtros utilizados na convolução: na terceira

camada, são utilizados filtros 5x1; na quarta, são utilizados filtros 3x1, e na quinta, utilizase filtros unitários 1x1. Na saída dessas três camadas, a dimensão da matriz de dados não é alterada, mantendo-se em 30x32.

Na sexta camada, chamada *flatten*, ocorre o achatamento da matriz 30x32 resultante da camada anterior, onde os dados são reorganizados de forma que as linhas são transpostas e colocadas uma abaixo da outra, resultando em um vetor de 960 linhas e 1 coluna.

A partir da sétima camada, tem-se uma estrutura de rede neural artificial simples, com 2 camadas densas e 1 camada de saída. A primeira camada densa é composta de 128 neurônios, a segunda por 64 neurônios e a camada de saída composta de um neurônio, que realiza a classificação dos dados através da função de ativação sigmóide, classificando entre 1, para indicar pico de fECG, e 0, para indicar a não ocorrência de pico de fECG.

Figura 18 – Arquitetura da Rede Neural Convolucional. FONTE: (JUNIOR, 2018)

## 4.3 Implementação da CNN em C no ARM

Para identificação dos gargalos computacionais do código em C da CNN proposta por (JUNIOR, 2018), optou-se pela execução do código em um processador ARM implementado em hardware que é mais apropriado, uma vez que em um co-projeto de hardware e software a parte de software comumente é executada por um microprocessador dedicado no SoC.

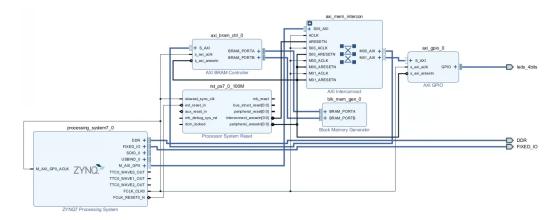

Sendo assim, foi instanciado um microprocessador ARM no SoC Zynq-7000 por meio da placa de desenvolvimento Zybo. Para instanciação foi utilizado a ferramenta de

Block Design do Vivado, onde foi projetado o bloco de processamento que inclui o IP do microprocessador Zynq e outros IPs adicionais como barramentos AXI, timers, blocos de memória e módulos de conexão GPIO. A figura 19 mostra o diagrama de blocos do microprocessador ARM instanciado.

Figura 19 – Diagrama de blocos do microprocessador ARM-Zynq instanciado como IP. FONTE: Autor.

A partir da validação do projeto do IP e implementação do design pelo Vivado, foi gerado o Bitstream do circuito e exportado como hardware para o software do XSDK.

No XSDK com o projeto criado para o microprocessador, foi incluído o arquivo do código em C da CNN e juntos com suas bibliotecas, os compiladores do SDK foram ajustado para reconhecimento de todas as funções utilizadas no código e também configurados conforme o tutorial de (AREIBI, 2020) para a implementação da análise de profile do código executado no microprocessador instanciado em hardware, que foi realizada pelo SDK e interpretada pelo gprof.

### 4.4 Descrição da Primeira Camada Convolucional em VHDL

As camadas convolucionais são as mais importantes da arquitetura de uma Rede Neural Convolucional, conforme estabelecido no capítulo 2.2. Além disso, são as camadas que mais exigem poder computacional, devido à enorme quantidade de iterações de multiplicações e somas, além das funções de ativação aplicadas em cada amostra da saída. Dessa forma, a aceleração de algoritmos em hardware foi feita inicialmente para a primeira camada convolucional da rede, pois esta apesar de não ser a camada de maior custo computacional da rede, é a que possui maior tamanho de filtros 7x1 e, uma vez que sua implementação seja bem sucedida, a replicação de sua estrutura para as outras camadas convolucionais se apresenta ser mais simples do que quando feito o contrário.

Os filtros, ou *kernel*, aplicados na primeira camada convolucional possuem função de realçar as principais características a serem extraídas das amostras de entradas que

contribuem para a classificação do pico de fECG. A definição do tamanho e dos valores dos filtros foram obtidos de (JUNIOR, 2018), onde estes foram formados por pesos inicializados aleatoriamente e atualizados durante o processo de backpropagation.

O algoritmo dessa camada pode ser analisado pelo código de sua função na linguagem C (vide Figura 20). Observa-se que o algoritmo consiste em *loops* iterativos, que realizam a convolução através da multiplicação das amostras (ajustadas) pelos filtros convolucionais e da soma dos resultados a cada 7 amostras, juntamente com o acréscimo de um bias, e aplicando ao resultado em cada amostra de saída a função de ativação RELU.

A função de ativação RELU é uma função não linear descrita na equação 4.1, onde quando o resultado da saída da camada for negativo o valor é convertido para zero e quando for maior ou igual a zero o valor de saída é mantido, logo tem-se uma redução de erros na classificação da amostra de entrada.

$$f(x) = \max(0, x) \tag{4.1}$$

Figura 20 – Cógido em C para a primeira camada convolucional. [numberOfFilters=32; sampleLength=60; firstFilterLength=7.] FONTE: Adaptado de (JUNIOR, 2018)

Pelo código da Figura 20, pode ser observado que dentro do *loop* mais interno tem-se a multiplicação por cada um dos 7 filtros a cada 7 amostras do ECG. Após cada multiplicação, o resultado é somado/acumulado e, após as 7 iterações, tem-se a saída para cada amostra da matriz resultante, onde é efetuada a soma com o bias e passa-se pela função de ativação. No próximo loop, as colunas são percorridas dentro de uma mesma linha da matriz, e no loop mais externo são percorridas as colunas.

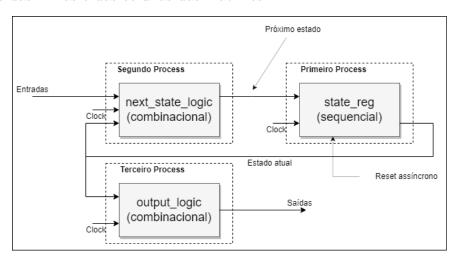

Para implementar em VHDL a função completa da camada convolucional, foi proposta uma arquitetura de projeto RTL (Register Transfer Level). A estratégia utilizada foi primeiramente, descrever o loop mais interno da função, que realiza a multiplicação e soma das entradas com os filtros, bias e função de ativação e posteriormente, instanciá-lo

como componente no módulo principal, e realizar as iterações dos *loops* externos, que percorre e varia as linhas e colunas das matrizes das amostras de entradas, filtros, bias e também na matriz de saída resultante da camada convolucional.

Vale ressaltar que o tamanho do conjunto de entradas, do bias, dos filtros e dos contadores que varrem os conjuntos de entrada e saída da camada convolucional, foram descritas de forma parametrizável, porém a quantidade de multiplicadores e somadores instanciados foi descrita de forma estática. Todos as constantes e parametrizações das entradas podem ser consultados no código VHDL da biblioteca *fpupack* do Apêndice A, tal biblioteca foi obtida de (MUNOZ D. F. SANCHEZ, 2010b), importada e adaptada no presente projeto, conforme necessidade.

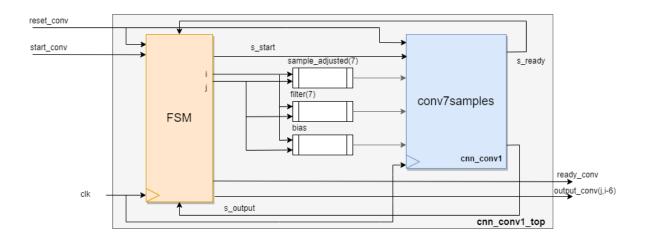

### 4.4.1 Componente do *loop* interno

Para descrição em VHDL do loop mais interno do código referência em C, foi aproveitada a paralelização do FPGA para tornar mais eficiente o processo das sucessivas multiplicações e somas.

A arquitetura RTL demonstrada na Figura 21 implementa a função do loop mais interno do algoritmo em C proposto por (JUNIOR, 2018). A entrada do bloco é coletada a cada 7 amostras do sinal de ECG, sinal este que é um conjunto 60 amostras, em um registrador de entrada serial e saída paralela (SIPO), A quantidade de 7 amostras como entrada do bloco vem da definição da própria arquitetura da CNN proposta, onde os filtros da primeira camada convolucional são de tamanho 7x1. Em seguida, cada amostra é multiplicada por cada um dos filtros. Assim, são utilizados 7 multiplicadores em paralelo no primeiro estágio. No segundo estágio, são utilizados 3 somadores (s0, s1 e s2) em paralelo que servem para somar o resultado das multiplicadores do estágio anterior, de 2 em 2. Como a quantidade de multiplicadores é impar, o último será somado no próximo estágio. No terceiro estágio, há mais 2 somadores (s3 e s4) em paralelo que acumulam o resultado de cada somador do estágio anterior e também o resultado da última multiplicação (m6). No quarto estágio, é somado o resultado de s3+s4 e, posteriormente, outro somador acrescenta o respectivo bias ao resultado. Por fim, tem-se a função comparadora RELU e então o resultado é registrado na matriz de saída da camada convolucional.

O bloco funcional implementado, chamado "cnn\_conv1", utiliza 7 multiplicadores e 7 somadores, que são baseados em máquinas de estados finitas sequenciais síncronas, onde cada multiplicador e cada somador são operadores aritméticos e trigonométricos, que trabalham com representação aritmética em ponto flutuante de 27 bits encapsulados em IPs desenvolvidos em VHDL e disponibilizados por (MUNOZ D. F. SANCHEZ, 2010b) e (MUNOZ D. F. SANCHEZ, 2010a), instanciado em forma de componente e conectado por meio de sinais, seguindo uma lógica sequencial para ativação de cada componente. A figura 22 mostra o esquemático RTL do bloco da convolução fornecido pela descrição do

Figura 21 – Arquitetura proposta para iteração do loop interno da primeira camada convolucional. FONTE: Autor.

código em VHDL. O código VHDL para implementação da arquitetura pode ser visto no Apêndice B.