Universidade de Brasília - UnB Faculdade do Gama - FGA Engenharia Eletrônica

# Implementação Eficiente de um Módulo de Detecção de Movimento em Vídeo para SoC FPGA

Autor: Leonardo Brandão Borges de Freitas

Orientador: Prof. Dr. Daniel Mauricio Muñoz Arboleda

(FGA/UnB)

Brasília, DF 2022

#### Leonardo Brandão Borges de Freitas

# Implementação Eficiente de um Módulo de Detecção de Movimento em Vídeo para SoC FPGA

Monografia submetida ao curso de graduação em Engenharia Eletrônica da Universidade de Brasília, como requisito parcial para obtenção do Título de Bacharel em Engenharia Eletrônica.

Universidade de Brasília - Un<br/>B Faculdade do Gama - FGA

Orientador: Prof. Dr. Daniel Mauricio Muñoz Arboleda (FGA/UnB)

Brasília, DF 2022

Leonardo Brandão Borges de Freitas

Implementação Eficiente de um Módulo de Detecção de Movimento em Vídeo para SoC FPGA/ Leonardo Brandão Borges de Freitas. – Brasília, DF, 2022-72 p. : il. (algumas color.) ; 30 cm.

Orientador: Prof. Dr. Daniel Mauricio Muñoz Arboleda (FGA/UnB)

Trabalho de Conclusão de Curso – Universidade de Brasília - Un<br/>B Faculdade do Gama - FGA , 2022.

1. Detecção de Movimento em Vídeo. 2. FPGA. I. Prof. Dr. Daniel Mauricio Muñoz Arboleda (FGA/UnB). II. Universidade de Brasília. III. Faculdade do Gama. IV. Implementação Eficiente de um Módulo de Detecção de Movimento em Vídeo para SoC FPGA

$CDU\ 02{:}141{:}005.6$

#### Leonardo Brandão Borges de Freitas

# Implementação Eficiente de um Módulo de Detecção de Movimento em Vídeo para SoC FPGA

Monografia submetida ao curso de graduação em Engenharia Eletrônica da Universidade de Brasília, como requisito parcial para obtenção do Título de Bacharel em Engenharia Eletrônica.

Trabalho aprovado. Brasília, DF, 11 de maio de 2022:

Prof. Dr. Daniel Mauricio Muñoz Arboleda (FGA/UnB) Orientador

Prof. Dr. Gilmar Silva Beserra (FGA/UnB) Convidado 1

Prof. Dr. Jones Yudi Mori Alves da Silva (ENM/FT/UNB) Convidado 2

Brasília, DF 2022

# Agradecimentos

Agradeço a minha família por proporcionar um ambiente de criação com muito amor, respeito e liberdade o que ajudou a me formar como ser humano. Agradeço aos meus professores e colegas pela participação ativa em minha formação escolar o que me ajudou a dar valor na educação e no conhecimento científico. Agradeço especialmente ao meu orientador Prof. Dr. Daniel por me ensinar e motivar na área de eletrônica digital e design de hardware, inclusive por me auxiliar na concepção deste trabalho. Agradeço também a toda a equipe da Associação GigaCandanga, principalmente ao meu amigo e tutor Dr. Paulo Ângelo que me incentiva todos os dias a investir em minha carreira profissional.

#### Resumo

Este trabalho propõe uma implementação eficiente para detecção de movimento em vídeo a partir de otimizações na técnica de diferenciação temporal e fatiamento das imagens em regiões de pixel, com objetivo de evitar falsos positivos na detecção de movimento causado pela projeção de sombras no cenário monitorado. O algoritmo desenvolvido foi descrito como uma máquina de estados finita, ou da sigla em inglês FSM, e validado primeiramente em software através de uma aplicação Python. Em seguida, o algoritmo foi codificado para linguagem de descrição de hardware, VHDL, com o auxilio da plataforma de desenvolvimento Vivado. O resultado da simulação comportamental indicou que o algoritmo proposto compara um par de frames, com dimensões de 640x480p, em menos de 13 ms, se garantido um novo pixels a cada 10ns, ou seja, conseguindo operar a quase 160fps. Em termos de implementação em hardware o algoritmo embarcado apresentou consumo energético de aproximadamente 0.02W e, em termos de consumo de recursos, utilizou apenas 12% das LUTs e 11% dos Flip-Flops disponíveis no SoC FPGA modelo PYNQ-Z2, utilizada no protótipo do projeto. Todavia, devido a utilização de um barramento AXI-Lite entre os ambientes de software, que captura e pre-processa as imagens, e hardware, que aplica o algoritmo de detecção de movimento, a velocidade de envio dos pixels de um ambiente para o outro se mostrou insuficiente para alcançar a velocidade da simulação comportamental. Porém, desconsiderando a velocidade de processamento, os resultados se mostraram semelhantes tanto na FSM em software via aplicação Python, quanto na simulação comportamental via Vivado e até mesmo quando embarcado na plataforma PYNQ-Z2, o que valida o funcionamento do algoritmo proposto.

Palavras-chave: Detecção de movimento em vídeo, Diferenciação temporal, FPGA, PYNQ.

### **Abstract**

This project offers an efficient implementation for movement detection on video, based on the optimization of the temporal differencing technique and slicing of pixel area of images, aiming to avoid false positives on movement detection resultant of shadow projections in the monitored scenario. The algorithm developed was described as a finite state machine, or FSM, and validated first in software through a Python application. Then, the algorithm was coded in hardware description language, VHDL, utilizing the development platform Vivado. The result of the behavior simulation shows that the offered algorithm compares a pair of frames, with dimensions of 640x480p, in less than 13ms, if guaranteed a new pixel every 10ns, making it able to work at almost 160fps. In hardware implementation terms, the embedded algorithm shows energy consumption around 0,02W and, in resource consumption terms, it utilized only 12% of the LUTs and 11% of the Flip-Flops available in the SoC FPGA model PYNQ-Z2, used in the project prototype. Although, due to the use of a data bus AXI-Lite between software environments, that capture and pre-process images, and hardware, that applies the movement detection algorithm, the pixel's sending speed from an environment to another was proven insufficient to reach the almost 160fps of the behavior simulation. But, disregarding the processing speed, the results were similar, both in the software in FSM through Python application, in the behavior simulation through Vivado and even when embedded in the PYNQ-Z2 platform, validating that the algorithm works.

**Key-words**: video motion detection, temporal differencing, FPGA, PYNQ.

# Lista de ilustrações

| Figura 1 – GigaView: Fluxograma Geral do <i>Core</i>                                           | 14 |

|------------------------------------------------------------------------------------------------|----|

| Figura 2 – Diagrama em alto nível do <i>Produtor de Frames</i>                                 | 15 |

| Figura 3 – Um exemplo do processo de aquisição de uma imagem digital. (Figura                  |    |

| retirada de (GONZALES; WOODS, 2008), pág. 51, Figura 2.15)                                     | 19 |

| Figura 4 – Alargamento de Contraste e Limiarização. (Figura retirada de (GON-                  |    |

| ZALES; WOODS, 2008), pág. 106, Figura 3.2)                                                     | 20 |

| Figura 5 – Filtragem espacial e Vizinhos próximos. (Figura retirada de (GONZA-                 |    |

| LES; WOODS, 2008), pág. 105, Figura 3.1)                                                       | 20 |

| Figura 6 – Exemplo do fluxo óptico (Figura retirada de (OPENCV, 2013))                         | 22 |

| Figura 7 – Arquitetura Genérica de uma FPGA (Figura retirada de (XILINX, 2018))                | 23 |

| Figura 8 – Exemplo de uma LUT e elementos de Memória em um CLB (Figura                         |    |

| retirada de (XILINX, 2017))                                                                    | 24 |

| Figura 9 – Arquitetura contemporânea de uma FPGA (Figura retirada de (XI-                      |    |

| LINX, 2018))                                                                                   | 24 |

| Figura 10 – Exemplo arquitetural de um SoC FPGA (Figura retirada de (XILINX,                   |    |

| 2021b))                                                                                        | 25 |

| Figura 11 – Diagrama Y proposto por Gajski e Kuhn (Figura retirada de (SCH-                    |    |

| LOSSER, 2001))                                                                                 | 26 |

| Figura 12 – Visão geral sobre o fluxo de desenvolvimento de um projeto digital                 |    |

| (Figura retirada de (XILINX, 2016))                                                            | 28 |

| Figura 13 – Diagrama de operação da thread CaptureNDetect                                      | 32 |

| Figura 14 – Kernel K da função cv.blur() (Figura retirada de (OPENCV, 2021b)) .                | 32 |

| Figura 15 – Laço do cálculo das médias das regiões de $pixels$                                 | 34 |

| Figura 16 – <i>chunks</i> de médias                                                            | 34 |

| Figura 17 – Laço de comparação do par de $frames$                                              | 35 |

| Figura 18 — Parâmetros do Fatiamento dos <i>Frames</i>                                         | 36 |

| Figura 19 – Estados: Init                                                                      | 37 |

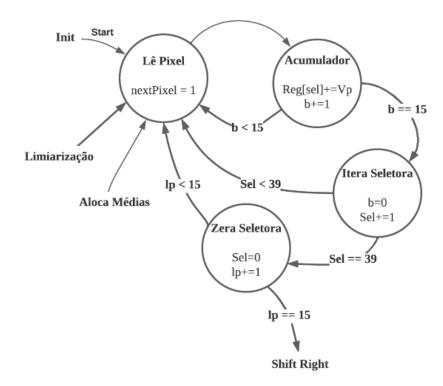

| Figura 20 — Estados: Lê Pixel, Acumulador, Itera Seletora e Zera Seletora                      | 38 |

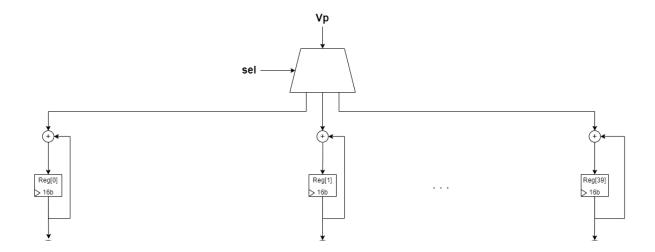

| Figura 21 – Diagrama RTL: Leitura e Acumulo de $pixels$                                        | 39 |

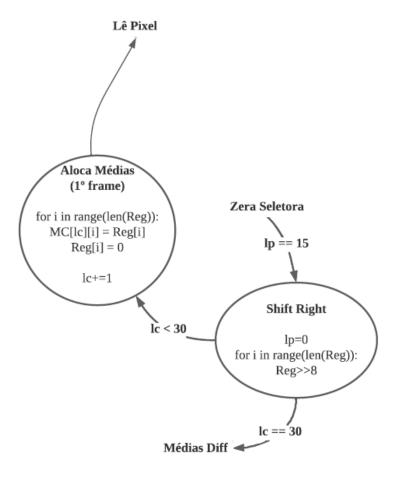

| Figura 22 – Estados: Shift Right e Aloca Médias                                                | 40 |

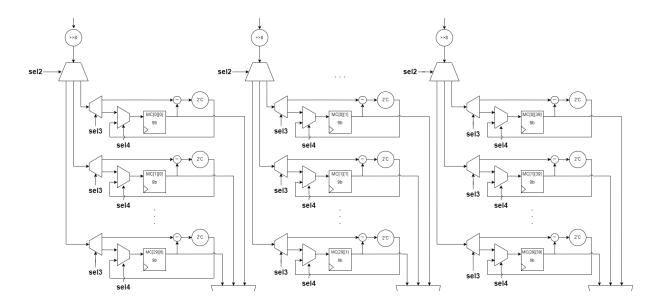

| Figura 23 — Diagrama RTL: cálculo e armazenamento das médias dos quadrantes $$ .               | 41 |

| Figura 24 – Estados: Médias Diff, Complemento de 2 e Limiarização $\ \ldots \ \ldots \ \ldots$ | 41 |

| Figura 25 – Diagrama RTL: Comparação e Limiarização                                            | 43 |

| Figura 26 – Estado: Verifica Movimento                                                         | 44 |

| Figura 27 – Diagrama RTL: Verificação de movimento                                             | 44 |

| Figura 28 – FSM Completa                                                                       | 45 |

| Figura 29 – | RTL Completo                                                                                           | 46 |

|-------------|--------------------------------------------------------------------------------------------------------|----|

| Figura 30 – | SoC FPGA modelo PYNQ Z2 (Figura retirada de (TUL, 2021))                                               | 49 |

| Figura 31 – | Exemplificação do barramento AXI. (figura retirada de (DEVELO-                                         |    |

|             | PER, 2022))                                                                                            | 50 |

| Figura 32 – | Block Design: PS, PL e periféricos                                                                     | 51 |

| Figura 33 – | Patamar inicial sem movimento ( $AM < 300$ )                                                           | 54 |

| Figura 34 – | Cena com movimento $(AM \ge 300)$                                                                      | 54 |

| Figura 35 – | Cena sem movimento $(AM < 300)$                                                                        | 55 |

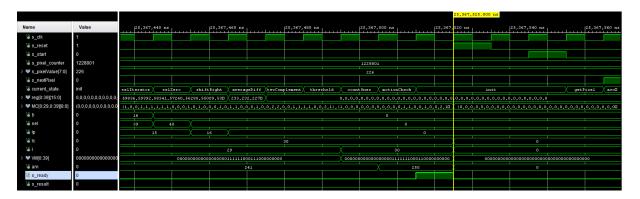

| Figura 36 – | Inicio da Simulação e reset acionado a 15 ns                                                           | 55 |

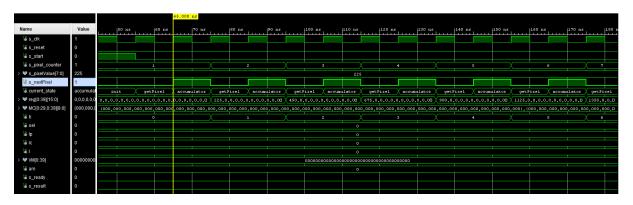

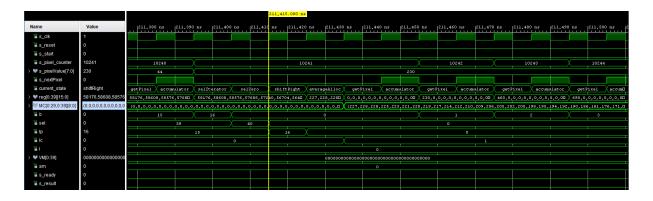

| Figura 37 – | Start acionado em 45 ns, inciando o ciclo de leitura e acumulo de pixels                               | 56 |

| Figura 38 – | nextPixel levantado em 65 ns. FSM preparada para acumular o valor                                      |    |

|             | do <i>pixel</i>                                                                                        | 56 |

| Figura 39 – | - Contador de bytes $b=15~{\rm em}$ 375 ns. FSM alcança o estado Itera Seletora                        | 56 |

| Figura 40 – | -sel = 1 em 385 ns. O pixels passam a ser acumulados na segunda                                        |    |

|             | posição de $reg[0:39]$                                                                                 | 57 |

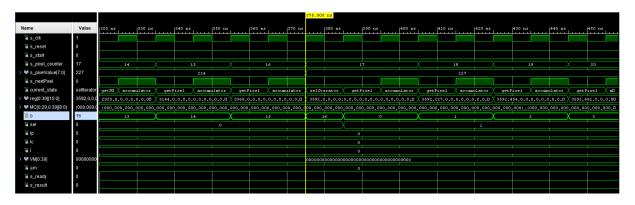

| Figura 41 – | $sel=39$ em 13.255 ns. Uma linha de $\it pixels$ completa foi acumulada                                | 58 |

| Figura 42 – | $lp=15,\ l_C<30$ em 211.415 ns. Médias armazenadas na primeira                                         |    |

|             | posição de $MC[0:29][0:39]$                                                                            | 58 |

| Figura 43 – | $l_{C}$ atinge 30 em 6.341.455 ns. Todos os 307200 $\it{pixels}$ lidos da primeira                     |    |

|             | imagem                                                                                                 | 58 |

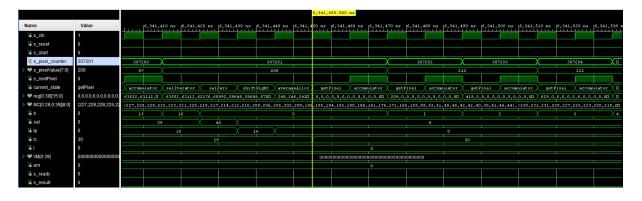

| Figura 44 – | - A primeira linha de <i>chunks</i> é subtraída entre a primeira e a segunda                           |    |

|             | imagem                                                                                                 | 59 |

| Figura 45 – | $l=1 \text{ em } 6.764.265 \text{ ns. } am=1 \text{ após } \mathbf{countOnes} \dots \dots \dots \dots$ | 60 |

| Figura 46 – | com 614.400 pixels lidos, como $am = 294$ , $result = 0 \dots \dots \dots$                             | 60 |

| Figura 47 – | Com 1.228.800 pixels lidos, como $am = 250$ , $result = 0$                                             | 61 |

| Figura 48 – | Com 1.843.200 pixels lidos, como $am = 1098$ , $result = 1 \dots \dots$                                | 61 |

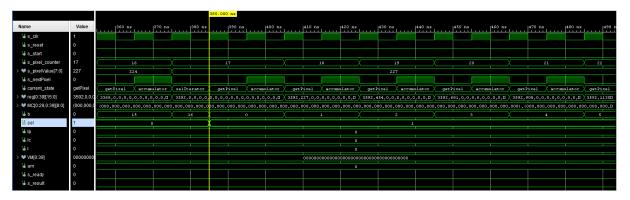

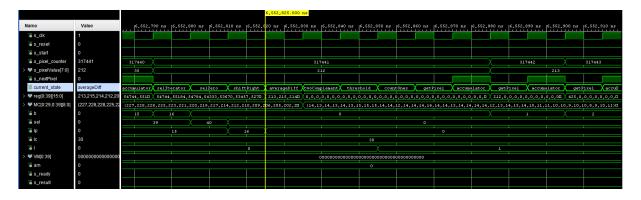

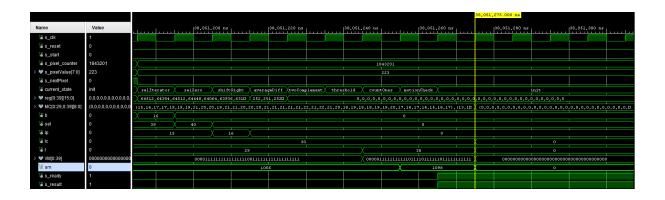

| Figura 49 – | Primeiro e segundo ciclo de comparação e limiarização do primeiro par                                  |    |

|             | de frames                                                                                              | 62 |

| Figura 50 – | Aos 614.400 pixels lidos, com $am = 294$ e $result = 0$                                                | 62 |

| Figura 51 – | Aos 1.228.800 pixels lidos, com $am = 250$ e $result = 0$                                              | 63 |

| Figura 52 – | Aos 1.843.200 pixels lidos, com $am = 1098$ e $result = 1 \dots \dots$                                 | 63 |

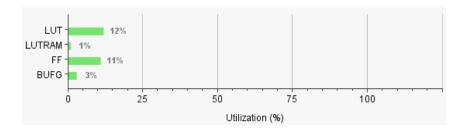

| Figura 53 – | Tabela com a utilização de recursos de HW do FPGA                                                      | 63 |

| Figura 54 – | Gráfico com a porcentagem da utilização de recursos de HW do FPGA                                      | 63 |

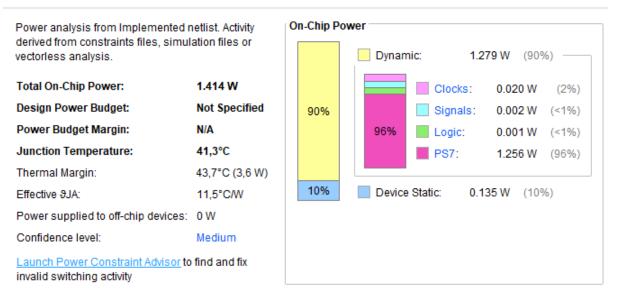

| Figura 55 – | Sumário de temporização do circuito implementado                                                       | 64 |

| Figura 56 – | Sumário de consumo energético do projeto                                                               | 64 |

| Figura 57 – | Estado para sincronização entre PS e PL                                                                | 65 |

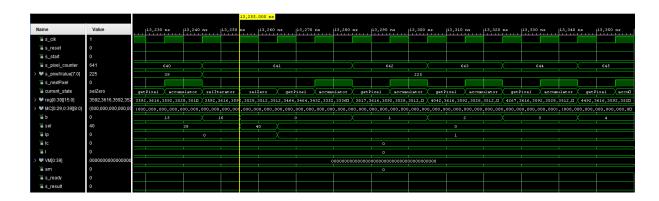

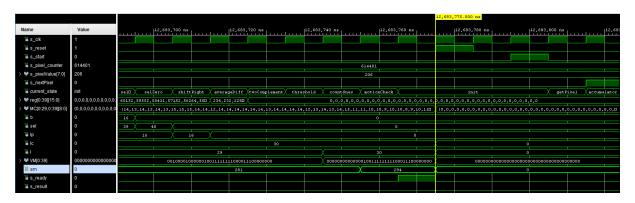

| Figura 58 – | - Aos 317440 pixels lidos ocorre a comparação da primeira linha de                                     |    |

|             | $chunks \text{ (am } = 0) \dots \dots \dots \dots \dots \dots \dots \dots \dots$                       | 66 |

|             |                                                                                                        |    |

| Figura 59 — Aos 327680 $pixels$ lidos ocorre a comparação da segunda linha de $chunks$ |    |  |  |  |

|----------------------------------------------------------------------------------------|----|--|--|--|

| (am = 1)                                                                               | 66 |  |  |  |

| Figura 60 – Aos 604160 $\it pixels$ lidos ocorre a comparação da penúltima linha de    |    |  |  |  |

| chunks (am = 281)                                                                      | 67 |  |  |  |

|                                                                                        |    |  |  |  |

# Lista de abreviaturas e siglas

SoC System on Chip

FPGA Field Programmable Gate Array

FSM Finite State Machine

CI Circuito Integrado

GPIO General Purpose Input/Output

IEEE Institute of Electrical and Electronic Engineers

CLB Configurable Logic Block

LUT Look-up Table

ASIC Application Specific Integrated Circuits

HDL Hardware Description Language

FPS Frames Per Second

dpi dots per inch

RTL Register Transfer Level

FIFO First In First Out

RTSP Real Time Streaming Protocol

MVP Minimum Viable Product

IoT Internet of Things

# Sumário

| 1     | INTRODUÇÃO                                   | 13 |

|-------|----------------------------------------------|----|

| 1.1   | Contextualização e Justificativa             | 13 |

| 1.2   | Produtor em alto nível                       | 15 |

| 1.3   | Objetivo geral                               | 17 |

| 1.3.1 | Objetivos específicos                        | 17 |

| 1.4   | Contribuições do Trabalho                    | 17 |

| 1.5   | Organização do Documento                     | 17 |

| 2     | FUNDAMENTAÇÃO TEÓRICA                        | 18 |

| 2.1   | Processamento Digital de Imagens             | 18 |

| 2.1.1 | Imagens Digitais                             | 18 |

| 2.1.2 | Aquisição de imagem                          | 18 |

| 2.1.3 | Processamento Espacial                       | 19 |

| 2.1.4 | Fluxo de Imagens ou Vídeo                    | 21 |

| 2.1.5 | Detecção de Movimento em vídeo               | 21 |

| 2.2   | Hardware Reconfigurável                      | 22 |

| 2.2.1 | Estrutura do FPGA                            | 22 |

| 2.2.2 | Estrutura de um SoC FPGA                     | 25 |

| 2.2.3 | Abstrações em Projetos de Circuitos Digitais | 26 |

| 2.2.4 | Fluxo de desenvolvimento do projeto          | 27 |

| 2.3   | Revisão do Estado da Arte                    | 28 |

| 3     | METODOLOGIA                                  | 31 |

| 3.1   | A Detecção de Movimento no Produtor          | 31 |

| 3.1.1 | Captura e Filtragem do Par de Imagens        | 31 |

| 3.1.2 | Fatiamento em regiões de <i>pixels</i>       | 32 |

| 3.1.3 | Diferença Absoluta e Limiarização            | 34 |

| 3.1.4 | Determinação de movimento                    | 35 |

| 3.2   | Proposta de Implementação Eficiente          | 35 |

| 3.2.1 | Pre-Definições                               | 36 |

| 3.2.2 | Captura e Preparação                         | 36 |

| 3.2.3 | Acumulo das intensidades por quadrante       | 37 |

| 3.2.4 | Valor médio do quadrante                     | 39 |

| 3.2.5 | Comparação e Limiarização                    | 41 |

| 3.2.6 | Verificador de Movimento                     | 43 |

| 3.2.7 | Máquina de Estados e RTL Completos           | 45 |

| 3.3   | Validação da FSM em Python                                |

|-------|-----------------------------------------------------------|

| 3.4   | Descrição de Hardware da FSM 47                           |

| 3.5   | Simulação Comportamental da FSM                           |

| 3.5.1 | Arquivo de <i>Pixels</i>                                  |

| 3.5.2 | Testbench                                                 |

| 3.6   | Protótipo na plataforma PYNQ-Z2                           |

| 3.6.1 | Motion Detector e AXI Lite (PL)                           |

| 3.6.2 | Programa do <i>Processing System</i>                      |

| 4     | RESULTADOS OBTIDOS                                        |

| 4.1   | Validação da Máquina de Estados em Software 53            |

| 4.2   | Resultados da Simulação Comportamental                    |

| 4.3   | Comparação entre a simulação comportamental em HW e SW 61 |

| 4.4   | Resultados da Implementação em <i>Hardware</i> 63         |

| 5     | CONCLUSÕES                                                |

|       | REFERÊNCIAS 70                                            |

### 1 Introdução

#### 1.1 Contextualização e Justificativa

A elevada densidade de habitantes em áreas urbanas tem intensificado problemas relacionados à segurança, mobilidade, saúde, meio ambiente, abastecimento, descarte de lixo, educação, desigualdade social, dentre outros. Por outro lado, a recente ascensão de tecnologias como IoT (Internet of Things) e visão computacional associadas ao processamento do grande fluxo de dados proveniente das metrópoles (big data) permitem a implementação de abordagens mais "inteligentes" e automatizadas àqueles problemas citados.

Não existe um consenso sobre o que de fato é uma cidade inteligente. Contudo, alguns pesquisadores associam o conceito ao investimento em tecnologias da informação e comunicação (TIC) (WEISS; BERNARDES; CONSONI, 2017). Além disso, outros pesquisadores afirmam que uma cidade inteligente é aquela capaz de impulsionar o crescimento econômico sustentável e incrementar a qualidade de vida de seus habitantes, com uma gestão inteligente dos recursos naturais e por meio de governança participativa (LAZZARETTI; SEHNEM; BENCKE, 2019).

Neste contexto, o projeto Campus Inteligente iniciado em 2018 pela Associação GigaCandanga visa de forma geral, e em primeiro momento, implementar tecnologias para coleta, processamento e armazenamento dos dados provenientes dos parâmetros ambientais e de usuários do campus Darcy Ribeiro da Universidade de Brasília, visando, principalmente, o incremento na qualidade de vida da população universitária. Não obstante, posteriormente, pretende-se expandir as soluções validadas na UnB para o Distrito Federal como um todo.

Indiferentemente dos conceitos adotados para definir o que é uma cidade inteligente, a infraestrutura de comunicação de dados, bem como as tecnologias utilizadas são fundamentais para implementar o conceito em questão. Para tanto, o projeto Campus Inteligente tem como objetivos:

- 1. Implementar conceitos de cidades inteligentes no espaço do campus Darcy Ribeiro da Universidade de Brasília a fim de testar as tecnologias e ferramentas existentes e efetivamente obter segurança, economia, acessibilidade e conforto nas dependências físicas do campus;

- 2. Contribuir com o engajamento de instituições e pesquisadores de diversas área a fim de consolidar um 'hub' de desenvolvimento tecnológico para, inicialmente, instalar

soluções em IoT, visão computacional e  $big\ data$  no maior campus universitário de Brasília.

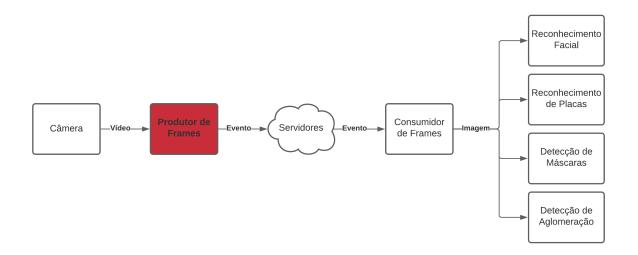

Tendo em vista os três pilares que compõem o escopo do projeto Campus inteligente: IoT, visão computacional e big data, tomou-se como ponto de partida o conceito de visão computacional, o que se concretizou no GigaView: Um sistema de monitoramento de vídeo inteligente, altamente escalável, que ao receber imagens de câmeras de vigilância, utiliza de algoritmos de Machine Learning para processar as imagens capturadas, resultando em produtos como, reconhecimento facial, reconhecimento de placas de automóveis, detecção de máscaras de proteção e detecção de aglomerações.

Figura 1 – GigaView: Fluxograma Geral do Core

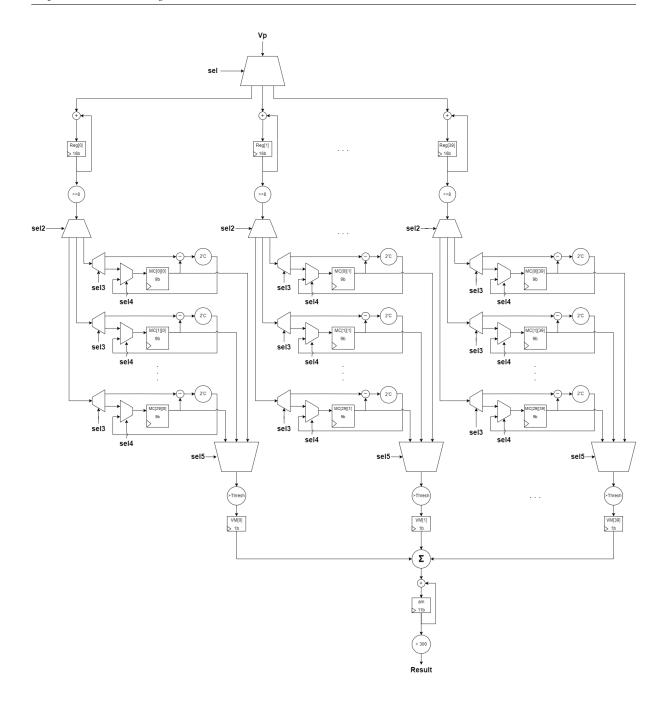

Neste contexto, a figura 1 sintetiza o fluxo operacional das principais entidades e micro serviços do núcleo de visão computacional do GigaView. Logo após a câmera, encontra-se o micro serviço chamado **Produtor de Frames**. Sendo a primeira entidade do núcleo do sistema, o Produtor recebe o *streaming* de vídeo em tempo real e aplica um algoritmo de detecção de movimento sobre pares de *frames*. Se houver movimento, o evento em vídeo é registrado nos servidores em nuvem. Uma vez armazenado, este evento é disponibilizado aos **Consumidores de Frames**, os quais separam as imagens dos vídeos e enviam quadro a quadro aos serviços de detecção e reconhecimento de objetos.

Em primeiro momento, visando a concepção de um produto mínimo viável (MVP) para validar as funcionalidades do GigaView, tanto o Produtor, quanto o Consumidor de Frames foram escritos em Python. Contudo, buscando a escalabilidade do projeto em grandes proporções, otimizações são necessárias para atingir um melhor desempenho e um menor consumo computacional por parte destes micro serviços que o compõem o core, ou núcleo do sistema. Para tanto, este trabalho propõe uma implementação eficiente dos serviços do **Produtor de Frames**, mais especificamente propõe descrever em hardware o algoritmo de detecção de movimento que se mostrou muito custoso em software para máquinas de propósito geral. Em que, embarcado em uma máquina virtual Linux Ubuntu 20.04, com 4 VCPUs de um processador core I7 da Intel e 8 Gb de memória RAM DDR4, uma instância do **Produtor de Frames** consome aproximadamente 12,5% do processador e 2% da memória RAM.

Ou seja, em termos de CPU, uma máquina com as características descritas acima suportaria apenas 8 **Produtores de Frames** simultâneos. Porém, no contexto de cidades, centenas ou até mesmo milhares de câmeras devem ser monitoradas ao mesmo tempo, o que exigiria um elevado investimento em recursos computacionais apenas para capturar eventos em vídeo derivados de movimento em cena.

#### 1.2 Produtor em alto nível

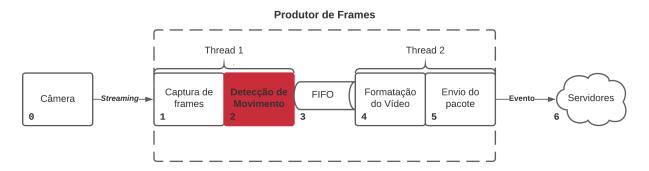

Em *software*, o **Produtor de Frames** orquestra duas *threads* computacionais: uma para capturar e detectar movimento e outra para formatar e enviar os eventos em vídeo para os servidores. A figura 2 apresenta as 5 etapas deste micro serviço.

Figura 2 – Diagrama em alto nível do *Produtor de Frames*

Ainda da figura 2, cada Produtor atende a apenas uma câmera, em 0, que disponibiliza seu streaming de vídeo através de um servidor RTSP (Real Time Streaming Protocol). A primeira thread, em 1, captura e armazena em memória um par de imagens por vez. A cada captura, os dois quadros são comparados, em 2, através da diferenciação temporal, que está melhor detalhada nas seções 2.1.5 e 3, determinando se houve ou não movimento a partir de um limiar pre definido. Em caso afirmativo, um intervalo de imagens direto do streaming da câmera é enfileirado em uma FIFO (First In First Out), em 3. Vale ressaltar que este intervalo de imagens enfileiradas é configurado em segundos de acordo com a demanda do usuário. Não obstante, ao receber os quadros na saída da fila, a segunda thread formata um arquivo de vídeo (MP4) com o intervalo de imagens, em 4, e envia o pacote aos servidores em 5. Este pacote contem não apenas o payload como vídeo, mas também o nome do arquivo como aviso para as demais entidades, bem como o registro temporal do evento para o banco de metadados.

As etapas 3, 4 e 5 acontecem apenas quando um movimento for identificado. Em outro caso permanecem em estado inativo e por isso exigem da CPU (Central Process Unit) de forma extraordinária. No entanto, as etapas 1 e 2 trabalham ininterruptamente, de forma dispendiosa para o processador. Uma das formas de reduzir a carga sobre o processador é diminuindo a velocidade de captura, em 1, espaçando no tempo o armazenamento em memória dos pares de imagens capturadas. De qualquer forma, há um consumo de memória associado ao armazenamento dos quadros, bem como um consumo associado ao tempo de processamento para o algoritmo de detecção de movimento, o que, como já citado anteriormente, exige uma capacidade computacional inviável para a escalabilidade do GigaView com um número elevado câmeras.

O uso de arquiteturas reconfiguráveis tais como FPGAs (Field Programmable Gate Arrays) permitem explorar o paralelismo intrínseco dos algoritmos de detecção de movimento em vídeo, acelerando a sua execução diretamente em hardware. Adicionalmente, dispositivos reconfiguráveis permitem a adaptabilidade das soluções de hardware em função das condições experimentais, de esforço computacional ou de consumo de energia. Uma característica importante dos dispositivos SoC (System on Chip) FPGA é que aproveitam a flexibilidade do software e a robustez computacional do hardware para obter soluções eficientes. Desta forma, é possível obter uma implementação eficiente do algoritmo de detecção de movimento, otimizando o **Produtor de Frames** em busca de baratear a escalabilidade da solução.

#### 1.3 Objetivo geral

Otimizar e descrever em *hardware* o algoritmo de detecção de movimento em vídeo do Produtor de Frames e embarca-lo em um *SoC FPGA* modelo PYNQ-Z2 com o intuito reduzir o consumo de recursos computacionais e o tempo de processamento da aplicação.

#### 1.3.1 Objetivos específicos

- 1. Otimizar o algoritmo de detecção de movimento do **Produtor de Frames**, modelandoo em uma FSM (*Finite State Machine*), buscando validar seu funcionamento primeiramente em uma aplicação Python em *software*.

- 2. Programar em VHDL o algoritmo previamente otimizado e testado em *software*, validando seu funcionamento por meio de simulações comportamentais no Vivado.

- Implementar o algoritmo descrito em VHDL e embarca-lo em um SoC FPGA modelo PYNQ-Z2.

- 4. Programar uma aplicação em *software* para o ARM do *SoC FPGA* que se comunique com o algoritmo de detecção de movimento em *hardware* e opere suas entradas e saídas em busca de validar seu funcionamento.

#### 1.4 Contribuições do Trabalho

Este trabalho propõe uma otimização na técnica de diferenciação temporal para detecção de movimento em vídeo. Uma arquitetura sistêmica foi elaborada a partir do algoritmo descrito em uma aplicação Python em software com o objetivo de atingir uma descrição comportamental em hardware derivada de um projeto RTL descrito em VHDL. Para tanto, experimentos e testes foram realizados sob os critérios de otimalidade de um projeto digital. Contribuindo com mais um modelo de detecção de movimento em vídeo para um SoC FPGA.

#### 1.5 Organização do Documento

Este documento propõem as etapas de desenvolvimento de um trabalho de conclusão de curso em engenharia eletrônica e descreve em 5 capítulos: a justificativa e os objetivos do projeto na introdução. A fundamentação teórica, no segundo capítulo, trata das técnicas utilizadas em processamento digital de imagens e também sobre *hardware* reconfigurável mais especificamente sobre a SoC FPGA da série Zynq-7000. O capítulo três trata sobre a metodologia aplicada na pesquisa. E os capítulos finais discutem sobre os resultados alcançados, bem como sobre a conclusão dos trabalhos realizados.

# 2 Fundamentação Teórica

Neste capítulo serão apresentados conceitos sobre a representação, a aquisição e o processamento digital de imagens, bem como sobre os métodos mais usuais para identificar movimento em vídeo. Além disso, será detalhada a estrutura de um  $SoC\ FPGA$  e, ao final do capítulo estão citados os trabalhos do estado da arte relacionados ao tema de pesquisa.

#### 2.1 Processamento Digital de Imagens

#### 2.1.1 Imagens Digitais

Considerando imagens em preto e branco, os autores em (GONZALES; WOODS, 2008) definem uma imagem como uma função bidimensional f(x, y), cuja amplitude, para qualquer par de coordenadas espaciais x e y, determina a **intensidade** ou a **escala de cinza** daquela imagem, naquele ponto. Não obstante, uma imagem é considerada digital quando, tanto o par de coordenadas (x, y), quanto suas respectivas intensidade possuem valores finitos e discretos. Para tanto, uma imagem digital é constituída por uma matriz de elementos finitos, os quais possuem um valor de intensidade e uma posição em particular dentro desta matriz. Estes elementos, chamados de *picture elements* ou de *pixels* são as partículas fundamentais de uma imagem digital.

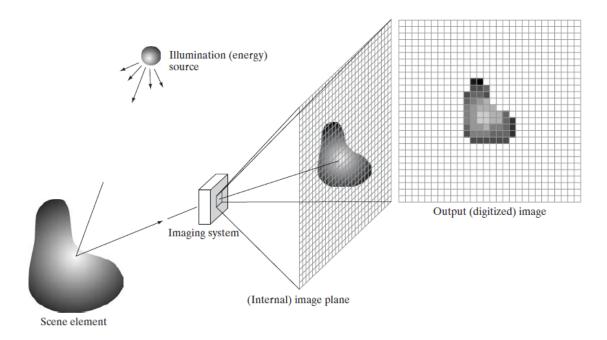

#### 2.1.2 Aquisição de imagem

As imagens digitais provêm de um cenário real, cujos objetos em cena, ao serem iluminado por um fonte, refletem ou absorvem diferentes comprimentos de luz. Estes fótons, ou a ausência deles, podem ser percebidos por um material fotossensível que traduz a partícula eletromagnética em um formato de onda em tensão elétrica. Para tanto, através de um computador, este sinal em tensão pode ser quantizado e, desta forma, compor um pixel do cenário. Ao organizar vários destes pixels em uma matriz, uma imagem digital é formada, assim como exemplificado no esquemático da figura 3.

Diferentes sistemas de aquisição de imagens, tais como as câmeras digitais, possuem diferentes parâmetros de **resolução espacial** e de **intensidade luminosa**. Ainda segundo (GONZALES; WOODS, 2008), a **resolução espacial** é definida como a menor medida discernível em uma imagem. O que, quantitativamente, pode ser expresso em quantidade de pontos por unidade de distância, do inglês: *dots per inch*, ou dpi. Além disso, os autores ainda define que a **resolução de intensidade** se dá pela menor variação discernível sobre os níveis de intensidade dos *pixels* que compõem a imagem.

Figura 3 – Um exemplo do processo de aquisição de uma imagem digital. (Figura retirada de (GONZALES; WOODS, 2008), pág. 51, Figura 2.15)

#### 2.1.3 Processamento Espacial

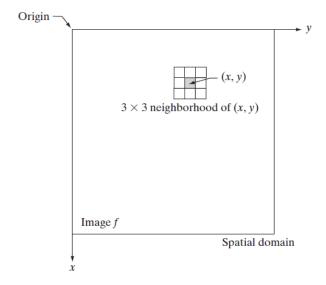

No domínio do espaço, processar uma imagem f(x,y) significa manipular diretamente seus pixels através de um operador T, gerando outra imagem g(x,y). Podendo ser expresso como:

$$g(x,y) = T(f(x,y)) \tag{2.1}$$

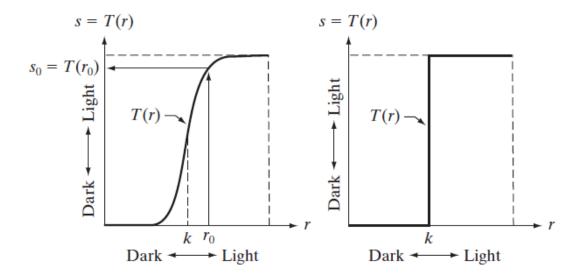

Existem duas categorias básicas em termos de processamento espacial de uma imagem, sendo elas: a transformação de intensidade e a filtragem espacial. O primeiro caso aplica um operador T sobre a intensidade individual 'r' de cada pixel, modificando-o para uma nova intensidade 's'. Ou seja, neste caso um elemento da imagem não interfere no outro, sendo a transformação de intensidade comumente utilizada na variação de contraste ou limiarização da imagem.

Observa-se do gráfico à esquerda na figura 4 que é possível gerar uma imagem com maior contraste, escurecendo os pixels com intensidade menor que um limiar k e também clareando os de intensidade maior que k. Todavia, do gráfico a direita da mesma figura, percebe-se que a imagem será binarizada pelo operador T. Ou seja, os pixels abaixo de k recebem a intensidade mínima, já os acima, recebem a intensidade máxima.

Figura 4 – Alargamento de Contraste e Limiarização. (Figura retirada de (GONZALES; WOODS, 2008), pág. 106, Figura 3.2)

A filtragem espacial, exemplificada pela figura 5, leva em consideração os valores de intensidade de uma janela de vizinhos próximos ao pixel que será operado por T. Esta janela, também conhecida como kernel, pode variar em tamanho de acordo com o filtro empregado, bem como nos pesos de contribuição dos vizinhos. Esta técnica de filtragem é comumente utilizada para suavizar ou destacar os contornos dos objetos na imagem, ou seja as áreas de alta frequência.

Figura 5 – Filtragem espacial e Vizinhos próximos. (Figura retirada de (GONZALES; WOODS, 2008), pág. 105, Figura 3.1)

Vale ressaltar que, ainda segundo (GONZALES; WOODS, 2008, sessão 3.1.1, pág. 105), o processamento espacial de imagens é geralmente mais eficiente e menos custoso computacionalmente quando comparado aos processamentos no domínio da frequência.

#### 2.1.4 Fluxo de Imagens ou Vídeo

Um vídeo nada mais é do que imagens capturadas e dispostas de forma sequencial com o intuito de imprimir movimento. Seja por uma câmera com fundo estático, onde objetos se deslocam, ou até mesmo pela movimentação da própria câmera, com fundo dinâmico. De qualquer forma, o vídeo herda os parâmetros de resolução das imagens que o compõe e, além disso, em termos da cadência no fluxo de imagem, é comum definir uma velocidade de captura, ou seja, a velocidade com que o vídeo se apresenta em quadros por segundo, da sigla em inglês: FPS (frames per second).

#### 2.1.5 Detecção de Movimento em vídeo

Seja para fugir de predadores ou até mesmo para identificar presas, desde que os primeiros aparatos ópticos se formaram na natureza é uma necessidade comum perceber o movimento através da variação na luz ambiental. Não obstante, com o advento das câmeras e da automação nos serviços de vigilância por vídeo, surge a necessidade de emular a detecção de movimento natural. Para tanto, existem diversas técnicas empregadas para responder às variações temporais e espaciais em vídeo causadas pelo movimento. De modo geral, as técnicas mais utilizadas baseiam-se em três princípios: subtração de fundo (back-ground subtraction), diferenciação temporal (temporal differencing) e fluxo óptico (optical flow).

A subtração de fundo é a técnica mais usual empregada sobre câmeras estáticas. O método se baseia em um modelo do fundo do cenário, comparando-o com as imagens capturadas. Desta forma, a subtração de fundo consegue detectar e isolar os objetos inseridos no quadro. Contudo, essa técnica não se adapta bem em ambientes dinâmicos com fundos muito variáveis. Em (SEHAIRI; CHOUIREB; MEUNIER, 2017) são citadas diversas técnicas com o intuito de corrigir os problemas derivados de um fundo dinâmico.

A diferenciação temporal é um das técnicas matematicamente mais simples e eficientes para detectar mudanças temporais na iluminação ao comparar quadros consecutivos no vídeo a partir da subtração da intensidade de seus *pixels*. Esta técnica se adapta muito bem a ambientes dinâmicos, porém não é possível, através da diferenciação temporal, isolar os objetos que se movem. Resultando apenas em uma identificação binária: se há ou se não há movimento em um intervalo de vídeo. Esse método é empregado no módulo de detecção de movimento de (MISHRA et al., 2011). Os autores em (SEHAIRI; CHOUI-REB; MEUNIER, 2017) detalham uma adaptação desta técnica que compara 3 *frames* consecutivos, conferindo robustez a ruídos e uma boa detecção para objetos que se movem lentamente.

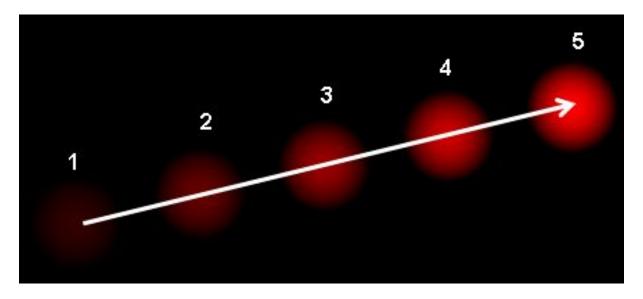

O fluxo óptico, por sua vez, possui o algoritmo mais complexo e custoso dentre as três técnicas citadas. Este método, assim como a diferenciação temporal, utiliza da dife-

rença entre quadros consecutivos, porém esse se preocupa em traçar um vetor indicando a direção e o sentido de movimento do objeto, tal como exemplificado pela figura 6, retirada de (OPENCV, 2013), onde o autor detalha o algoritmo Lucas-Kanade para aplicar o fluxo óptico como classificador de movimento em vídeo.

Figura 6 – Exemplo do fluxo óptico (Figura retirada de (OPENCV, 2013))

Para tanto, considerando que o engatilhador de captura do **Produtor de Frames** não se preocupa com o formato dos objetos em cena, nem mesmo com a direção do movimento, este trabalho descreve uma variação na técnica de **diferenciação temporal**, detalhada no capítulo 3, em busca de simplicidade matemática, para reduzir o tempo de processamento, e também em busca de eficiência no armazenamento das imagens capturadas, para reduzir o consumo de memória.

#### 2.2 Hardware Reconfigurável

Os FPGAs, sigla em inglês para Field Programmable Gate Array, surgiram em meio aos circuitos integrados de aplicação específica (ASIC) para facilitar a descrição de hardware (HDL), trazendo o conceito de circuitos reconfiguráveis. Estes dispositivos desvincularam os blocos pre-programáveis do fabricante de ASICs, dando aos projetistas a possibilidade de criar blocos funcionais dedicados especificamente aos seus projetos.

#### 2.2.1 Estrutura do FPGA

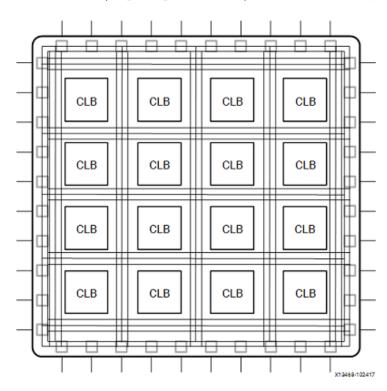

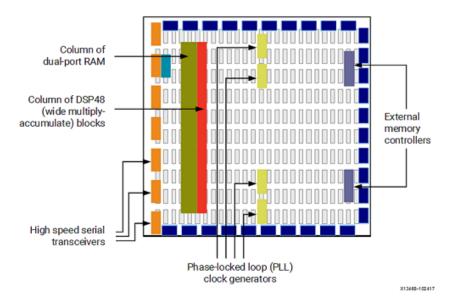

A estrutura básica de um FPGA consiste em dispor um grande número de portas lógicas em um arranjo matricial chamado de **Bloco Lógico Configurável**, ou da sigla em inglês CLB. Estes CLBs são rodeados por **Trilhas de Roteamento** multiplexadas

que os comunicam entre si e também permitem a a entrada ou saída de sinais através dos  $\mathbf{M\acute{o}dulos}\ \mathbf{I/O}$  (vide figura 7).

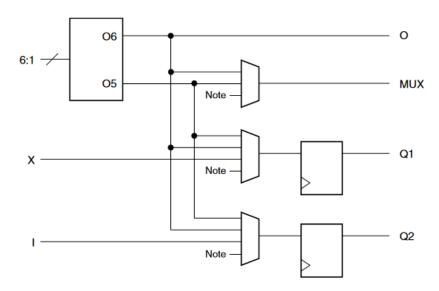

Um CLB é como uma célula tronco para FPGA. Se especializa a partir de uma tabela verdade, ou também conhecida como Look-up table (LUT) que relaciona os valores de entrada a um possível resultado na saída, armazenando-o em registradores Flip-Flops. Estas células são extremamente versáteis, tornando flexível o particionamento e o mapeamento da lógica digital pela FPGA, além de serem consultados de forma concorrente, o que os torna potencialmente úteis para processamento paralelo. A figura 8 a seguir exemplifica um CLB composto por uma LUT de 6 entradas e duas saída que podem ser roteadas diretamente ao próximo CLB, através da rota 'O' e 'MUX', ou multiplexadas para as unidades de memória (Flip-Flops ou Latch) com saídas em 'Q1' e 'Q2'.

Figura 7 – Arquitetura Genérica de uma FPGA (Figura retirada de (XILINX, 2018))

Figura 8 – Exemplo de uma LUT e elementos de Memória em um CLB (Figura retirada de (XILINX, 2017))

Os modelos mais atuais de FPGAs possuem variados ASIC integrados, tais como: blocos de RAM, FIFOs, blocos DSPs (*Digital Signal Processing*), conversores de dados ADCs, PLLs, Clock Managment, processadores ARM e até mesmo os *softprocessor*, uBlaze e PicoBlaze que são processadores construídos a partir dos próprios CLBs, BRAMs e DSPs do FPGA. A figura 9 exemplifica um modelo de FPGA atual.

Figura 9 – Arquitetura contemporânea de uma FPGA (Figura retirada de (XILINX, 2018))

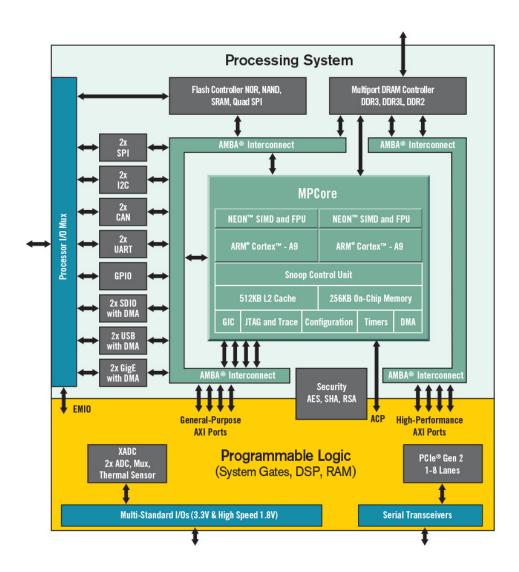

#### 2.2.2 Estrutura de um SoC FPGA

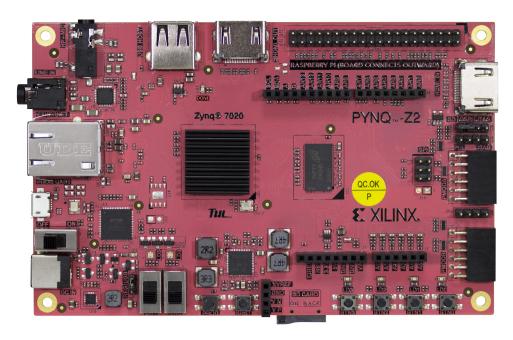

O conceito por trás de um SoC FPGA é unir a velocidade de processamento e robustez de um FPGA com a flexibilidade de um CPU e seus periféricos de aplicação específica. Um exemplo é o SoC Zynq-7000 da Xilinx, que possui um processador ARM Cortex A9 Dual Core que dispõe de memória Cache com 512kb, dois barramentos de comunicação para cada protocolo Machine to Machine: UART, I2C e SPI, interfaces GPIO e USB, e também espaços em memória DRAM. Todas essa funcionalidades no mesmo chip, bem como a possibilidade de embarcar aplicações em software, facilitam a programação e os testes dos projetos descritos em hardware. A figura 10 exemplifica um SoC FPGA do modelo Zynq-7000.

Figura 10 – Exemplo arquitetural de um SoC FPGA (Figura retirada de (XILINX, 2021b))

#### 2.2.3 Abstrações em Projetos de Circuitos Digitais

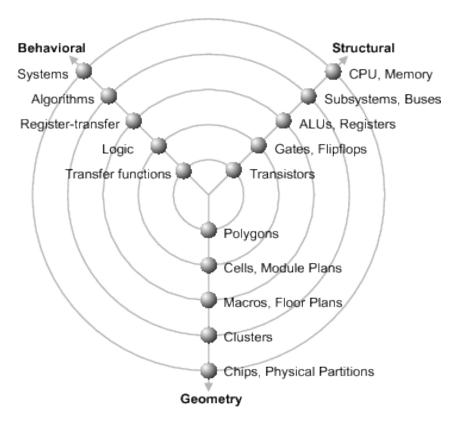

O modelo de Gajski-Kuhn descreve um projeto de circuito integrado em três eixos principais: Comportamental, Estrutural e Físico. O primeiro eixo ou domínio descreve o projeto em termos de blocos comportamentais, mas não se preocupa em como atingir suas funcionalidades internas. O segundo domínio se preocupa com as ligações e estruturas básicas que compõem os blocos funcionais. Não obstante, o domínio físico descreve o projeto enquanto disposição geométrica de seus módulos ou componentes, voltada para fabricação do circuito.

Assim como mostrado na figura 11, os domínios são dispostos em 3 eixos que formatam um 'Y'. Ao adentrar para o centro do gráfico, o nível de abstração diminui e a complexidade do projeto aumenta.

Figura 11 – Diagrama Y proposto por Gajski e Kuhn (Figura retirada de (SCHLOSSER, 2001))

Os 5 níveis de abstração estão representados pelos círculos ao redor dos domínios em 'Y'. Levando o projeto de uma abstração **Sistêmica** de altíssimo nível, geralmente lançando mão sobre projetos integrados entre *software* e *hardware* (HW/SW) para determinar se o sistema é viável.

Passando para abstração **Arquitetural** que simula o algoritmo de alto nível em alguma linguagem de descrição de hardware como HDL.

Fazendo possíveis otimizações na camada de abstração **Lógica**, onde as especificações funcionais do nível anterior são traduzidas em portas lógicas com o intuito de reduzir a quantidade de elementos biestáveis e acrescentar desempenho no projeto.

Para finalmente alcançar a camada **Física** que descreve o conjunto completo de informações necessárias à construção do circuito digital. Nesta última camada o projetista pode aplicar uma mascara de CI, traduzindo as funções lógicas em geométricas.

#### 2.2.4 Fluxo de desenvolvimento do projeto

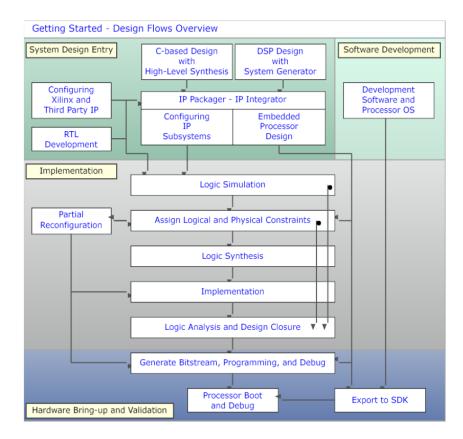

Em projeto digitais é comum orientar o desenvolvimento do trabalho a partir de um referencial *top-down*: partindo da abstração sistêmica e comportamental do projeto até alcançar as otimizações na camada física do circuito. Tratando-se de um projeto para FPGA a figura 12 apresenta uma visão geral sobre as etapas sugeridas pela Xilinx para construção de um projeto digital em hardware.

Após desenhar o projeto de forma sistêmica, o projetista escreve e testa o algoritmo em software para validar o projeto a nível comportamental. Em seguida ocorre a síntese em alto nível que descreve o comportamento do algoritmo em termos de fluxo de sinais ou transferência de dados entre registradores e blocos de operação lógica, chamado de RTL (Register Transfer Level) que é escrito em alguma linguagem de descrição de hardware (HDL). Neste ponto o projeto RTL é testado através de simulações comportamentais para possíveis ajuste e otimizações. Então, os módulos validados no projeto RTL passam pelo processo de síntese lógica que os traduzem para o nível de portas lógicas. Com as portas lógicas definidas ocorre o processo chamado de Place and Route que organiza de forma estrutural o posicionamento e as ligações entre os módulos lógicos e os registradores. Neste ponto, o projetista pode reposicionar os componentes para facilitar a comunicação entre os módulos mais críticos e também otimizar o tamanho do circuito lançando mão sobre ferramentas de análise de temporização do circuito antes de exporta-lo. Finalmente, na última etapa o bitstream do circuito é gerado e os testes físicos podem ser realizados. No caso de desenvolvimento hardware-software, um novo fluxo de projeto relacionado com o desenvolvimento da aplicação de software é iniciado, por exemplo, usando o SDK.

Figura 12 – Visão geral sobre o fluxo de desenvolvimento de um projeto digital (Figura retirada de (XILINX, 2016))

#### 2.3 Revisão do Estado da Arte

Nesta seção será disposto um panorama geral sobre os trabalhos relacionados a detecção de movimento em vídeo com base em FPGA. Independentemente da aplicação fim, os trabalhos encontrados acerca deste tema seguem etapas semelhantes para alcançar os resultados, sendo as principais: Aquisição e tratamento das imagens, aplicação do algoritmo de detecção, aplicação dos resultados e análise de temporização e consumo energético do projeto. Vale ressaltar que dentre os trabalhos aqui citados é comum a utilização de desenvolvimento entre a validação dos algoritmos em software e a sua aceleração em hardware (co-design HW/SW).

Os autores em (COTHEREAU; DELAITE; GOURDIN, 2008) iniciam os trabalhos com um estudo bem detalhado sobre os paradigmas de desenvolvimento de hardware utilizados na pesquisa, bem como comparando modelos de FPGA entre as fabricantes Altera e Xilinx. No entanto, o foco principal da pesquisa é verificar a possibilidade de criar um sistema de vigilância de vídeo sobre uma FPGA. Neste contexto, eles implementaram a aquisição de imagens de uma câmera IP através de entidades escritas em Verilog para uma FPGA modelo DE2 da Altera e além disso as imagens capturadas passam por um algoritmo de subtração de fundo escrito em C e embarcado no processador softcore Nios II disponível na placa de desenvolvimento escolhida. Contudo, eles relatam muitos

problemas de concorrência entre as entidades descritas em hardware e o algoritmo em software ao acessar as imagens em memória.

Em (JAGDALE; VAIDYA, 2012) os autores utilizam de uma câmera do modelo "TRDB-D5M" com resolução de 2592x1944p e que representa as imagens no modelo Bayer. O sensor é conectado diretamente nos GPIOs do Soc FPGA modelo DE-II 70 da Altera e configurado via protocolo I2C. Devido a representação padrão da câmera o algoritmo proposto nesta pesquisa primeiro converte de Bayer para RGB e depois para escala de cinza. Assim como em (COTHEREAU; DELAITE; GOURDIN, 2008) a detecção de movimento se dá pela técnica de subtração de fundo escrita em C e embarcada no softcore Nios II. Contudo neste projeto uma FIFO foi colocada entre o bloco de captura e o bloco de detecção de movimento para enfileirar as imagens capturadas e evitar a concorrência no acesso à memória observado na pesquisa anterior.

Os trabalhos realizados em (SINGH; SHEKHAR; VOHRA, 2016) alcançaram um protótipo para um sistema de vigilância automático baseado na detecção de movimento em vídeo e implementado na Virtex-5 da Xilinx modelo FX130T. Os autores utilizam uma variação da técnica de diferenciação temporal sobre 4 quadros consecutivos do vídeo. Este quadros são separados em blocos de *pixels* para o cálculo da média da região delimitada pelo bloco, o que torna o algoritmo menos sensível a cenários pseudo estacionários, ou seja aqueles cenários com muita variação luminosa causada por projeção de sombras.

O modelo para detecção de movimento em vídeo proposta em (JUNIOR et al., 2017) é baseada em uma técnica de fluxo ótico que capta o cenário a partir de dois sensores A e B. As imagens de apenas 320x240p formadas pelos dois sensores passam por um módulo chamado de EMD (Elementary Motion Detector), vide (JUNIOR et al., 2017, fig. 2), que filtra as entradas através de um passa baixas e calcula a diferença entre a correlação de A e de B. Desta maneira o EMD consegue determinar se um objeto se move para a direita ou para a esquerda. Aqui os autores simulam o algoritmo através dos software MatLab e Simulink, mas convertem os blocos simulados para VHDL e embarcam o algoritmo em uma Spartan-6 da Xilinx. Como resultados os autores conseguem identificar carros em movimento em uma rodovia, inclusive conseguindo separar as sombras projetadas sobre a pista dos veículos que as geram. Vale ressaltar que neste trabalho os autores não queriam apenas detectar o movimento em sí, mas determinar e rastrear no vídeo os objetos que se movem, vide (JUNIOR et al., 2017, fig. 5)

Devic; Serackis; Plonis, 2018) propõem uma estrutura de hardware para rastreamento de objetos em vídeo. Todavia, no trabalho em questão as imagens são capturadas a 60 fps e com resolução de 640x480p. Além disso, o algoritmo proposto em software é capaz de interagir com o usuário que escolhe um objeto em cena para ser demarcado e localizado ao longo do vídeo. Para isso os autores utilizam das técnicas HOG (Histogram

of Oriented Gradient) e LBP (Local Binary Pattern) para identificar a forma e a textura do objeto rastreado. Não obstante, ao embarcar o algoritmo em um FPGA Virtex 4 da Xilinx em VHDL é a detecção de movimento que seleciona o objeto a ser rastreado em cena. A detecção é semelhante ao proposto em (SINGH; SHEKHAR; VOHRA, 2016) em que as imagens são separadas em blocos de pixels para o cálculo da média daquela região e a diferenciação temporal é aplicada entre as regiões de imagens consecutivas. Os teste mostraram a robustez do algoritmo proposto utilizando um clock de apenas 25Mhz no FPGA.

### 3 Metodologia

Neste capítulo, serão tratados os métodos e os modelos utilizados para a implementação e teste do projeto. Tendo em vista a descrição sistêmica do Produtor de Frames em 1.2, a seção 3.1 detalha a detecção de movimento em vídeo utilizada por essa entidade. Em seguida, a seção 3.2 descreve uma proposta de implementação eficiente para o algoritmo de detecção de movimento em vídeo do Produtor de Frames, através de um diagrama de estados, ou FSM (*Finite State Machine*), e seu diagrama RTL equivalente, propondo otimizações para reduzir o consumo de recursos de *hardware*, bem como, acelerar o algoritmo. A seção 3.3 descreve uma aplicação Python destinada a validar o funcionamento da FSM em *software*. Na sequência, a seção 3.4, detalha a descrição de *hardware* do algoritmo proposto, em VHDL, através da plataforma Vivado. A seção 3.5, por sua vez, apresenta a metodologia empregada na simulação comportamental da FSM em VHDL. Finalmente, a seção 3.6 descreve os procedimentos para implementação física da FSM através da plataforma de desenvolvimento PYNQ.

#### 3.1 A Detecção de Movimento no Produtor

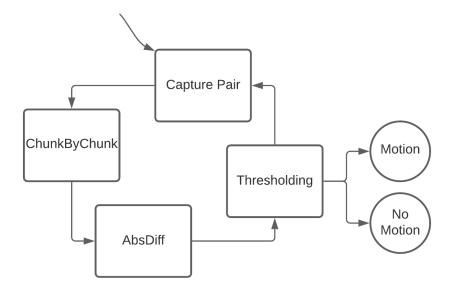

Dentro do **Produtor de Frames** existe uma thread que executa o método chamado CaptureNDetect. Este método aplica a diferenciação temporal entre dois frames através de 4 funções principais (vide figura 13): a primeira captura um par de imagens, a segunda fatia as imagens em regiões de pixels, a terceira calcula a diferença absoluta entre estas regiões, e a última verifica um limiar para determinar em quantas delas houve movimento. Se houver em pelo menos 25% das regiões, a flag de movimento é levantada. Caso contrário a flag de não movimento que é levantada.

#### 3.1.1 Captura e Filtragem do Par de Imagens

Para capturar um par de imagens, a aplicação executa um objeto capturador de vídeo da OpenCV (OPENCV, 2021a) que através de um socket RTSP (Real Time Streaming Protocol) se comunica com apenas uma câmera em rede TCP/IP. Após a captura, as imagens em memória sofrem uma transformação de intensidade para escala de cinza o que reduz o vetor de intensidade RGB dos pixels para um único valor de intensidade representado em 8bits, ou seja, alcançando valores inteiros de 0 até 255. Além disso, os contornos nas imagens são suavizados sob a aplicação de um filtro espacial de borramento com um kernel quadrado de lado 5 e peso 1/25 (vide figura 14). A convolução entre este kernel e a matriz que compõe os quadros reduz o contraste entre os pixels da imagem,

Figura 13 – Diagrama de operação da thread CaptureNDetect.

tornando-a mais homogênea em termos de intensidade, o que diminui os falsos positivos provenientes da diferenciação temporal.

$$\mathtt{K} = rac{1}{\mathtt{ksize.width*ksize.height}} egin{bmatrix} 1 & 1 & 1 & \cdots & 1 & 1 \ 1 & 1 & 1 & \cdots & 1 & 1 \ \dots & & & & & \ 1 & 1 & 1 & \cdots & 1 & 1 \end{bmatrix}$$

Figura 14 – Kernel K da função cv.blur() (Figura retirada de (OPENCV, 2021b))

Vale mencionar que em (OPENCV, 2021c) são detalhadas algumas funções para suavização de imagens através do OpenCV.

#### 3.1.2 Fatiamento em regiões de *pixels*

Na detecção de movimento através da diferenciação temporal é calculado o módulo da subtração entre o pixel na posição (x,y) da imagem anterior  $I_{t-1}$  e o pixel na mesma posição da imagem atual  $I_t$ , de acordo com a equação 3.1 a seguir:

$$\Delta P = |I_{t-1}(x, y) - I_t(x, y)| \tag{3.1}$$

Desta maneira, para afirmar se houve movimento é levado em consideração a diferença absoluta de cada um dos elementos entre as imagens. Contudo, em um cenário

outdoor sob a projeção de sombras que podem ser geradas por árvores ao vento ou por nuvens que bloqueiam o sol de tempos em tempos, foi verificado que a análise isolada de cada um dos pixels resulta em variações muito discrepantes entre os quadro comparados. Isto torna a detecção de movimento muito sensível à sombras e engatilha falsos positivos.

Neste contexto, o fatiamento das imagens foi uma estratégia adotada para lidar com as áreas de demasiada oscilação na intensidade dos *pixels* afetados por sombras. Após definido um número de linhas e de colunas que dividem as imagens em regiões, ou *chunks*, calcula-se a média de intensidade dos *pixels* destas regiões. Para tal procedimento, primeiramente são calculados dois coeficientes que relacionam, respectivamente, a quantidade de linhas e colunas do fatiamento com o comprimento e a largura das imagens, de acordo com as equações a seguir.

$$L = \frac{comprimento}{Linhas} \tag{3.2}$$

$$C = \frac{largura}{Colunas} \tag{3.3}$$

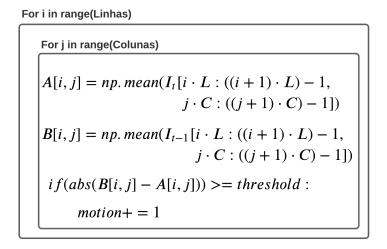

De acordo com o diagrama da figura 15, após calcular os coeficientes através das equações 3.2 e 3.3, o programa executa dois laços de repetição aninhados para percorrer os vetores bidimensionais  $I_t[comprimento, largura]$  e  $I_{t-1}[comprimento, largura]$  que armazenam as imagens em memória. Para cada região é calculada a média das intensidades dos pixels através do método 'np.mean()' (COMMUNITY, 2021) da biblioteca Numpy, alocando os resultados em outras duas matrizes: A[Linhas, Colunas] para imagem atual e B[Linhas, Colunas] para imagem anterior.

#### For i in range(Linhas)

For j in range(Colunas)

$$A[i,j] = np. \ mean(I_t[i \cdot L : ((i+1) \cdot L) - 1, \\ j \cdot C : ((j+1) \cdot C) - 1])$$

$$B[i,j] = np. \ mean(I_{t-1}[i \cdot L : ((i+1) \cdot L) - 1, \\ j \cdot C : ((j+1) \cdot C) - 1])$$

Figura 15 – Laço do cálculo das médias das regiões de pixels

Originalmente, o programa captura imagens com 1280 pixels de comprimento e 720 pixels de largura divididas em 4 linhas e 4 colunas. Para tanto, os coeficientes provenientes das equações 3.2 e 3.3 são dados por L=320 e C=180. Nesta configuração, a primeira iteração do laço aninhado aloca na primeira posição do vetor A[0,0] a média da região  $I_t[0:319,0:179]$  da imagem atual. Em seguida, ocorre o mesmo procedimento para a mesma região na imagem anterior  $I_{t-1}[0:319,0:179]$ , porém armazenando o resultado na primeira posição do vetor B[0,0]. A figura 16 imprime as duas matrizes A e B preenchidas com as médias das 16 regiões de pixels do par capturado.

| A[4,4] |        |        |        | B[4, 4] |        |        |        |        |

|--------|--------|--------|--------|---------|--------|--------|--------|--------|

|        | A[0,0] | A[0,1] | A[0,2] | A[0,3]  | B[0,0] | B[0,1] | B[0,2] | B[0,3] |

|        | A[1,0] | A[1,1] | A[1,2] | A[1,3]  | B[1,0] | B[1,1] | B[1,2] | B[1,3] |

|        | A[2,0] | A[2,1] | A[2,2] | A[2,3]  | B[2,0] | B[2,1] | B[2,2] | B[2,3] |

|        | A[3,0] | A[3,1] | A[3,2] | A[3,3]  | B[3,0] | B[3,1] | B[3,2] | B[3,3] |

Figura 16 – *chunks* de médias

#### 3.1.3 Diferença Absoluta e Limiarização

Após determinar as médias da região o programa aplica a diferença absoluta entre estes valores através da função abs(B[i,j]-A[i,j]) (FOUNDATION, 2021), determinando o módulo da variação média de intensidades daquela região entre os quadros capturados. Em seguida este módulo é comparado a um limiar pre-determinado pelo usuário que

indica a sensibilidade da detecção de movimento (vide figura 17). Ou seja, se o módulo calculado for maior ou igual ao limiar, determina-se que houve movimento naquela região incrementando em uma unidade uma variável que conta a quantidade de *chunks* com movimento.

Figura 17 – Laço de comparação do par de frames

Portanto, ao finalizar o laço aninhado da figura 17 o contador *motion* pode armazenar um valor entre 0 a 16, indicando no primeiro caso que não houve movimento em nenhuma região das imagens comparadas ou, para o segundo caso, que houve movimento em todas as regiões comparadas.

#### 3.1.4 Determinação de movimento

Por padrão o **Produtor de Frames** espera que ao menos um quarto dos *chunks* indiquem movimento para levantar a *flag* de movimento. Então, após a limiarização dos módulos calculados, se o contador *motion* for maior ou igual a 4, um trecho do *streaming* da câmera, com intervalo de tempo determinado pelo usuário na execução do programa, é armazenado em um arquivo de vídeo e enviado ao servidores. Caso contrário, o algoritmo volta a capturar um par de imagens, reiniciando a operação da *CaptureNDetect* descrita no diagrama da figura 13.

#### 3.2 Proposta de Implementação Eficiente

Este trabalho propõe, em primeiro momento, otimizar e testar em *software* o algoritmo da *CaptureNDetect* do **Produtor de Frames**. Contudo, como o objetivo principal da pesquisa é desenvolver um módulo de detecção de movimento para um *SoC FPGA*, uma FSM foi descrita em alto nível visando a implementação em *hardware*, bem como minimizar a quantidade de operações e o consumo de memória provenientes da técnica de

diferenciação temporal descrito na seção anterior. Para tanto, nesta seção serão apresentadas as etapas propostas para uma implementação eficiente da detecção de movimento em vídeo através da diferenciação temporal destinada a um  $SoC\ FPGA$ , mas que será validada em primeiro momento através de um programa base em software e, em seguida, o algoritmo validado, será descrito em HDL destinado a um  $SoC\ FPGA$  modelo PYNQ. Os resultados das duas etapas de desenvolvimento estão apresentados no capítulo 4.

#### 3.2.1 Pre-Definições

Para construção do algoritmo foi definido que as imagens teriam dimensões de 640x480p. Além disso, os quadros capturados serão fatiados em 40 colunas e 30 linhas totalizando 1200 *chunks* com dimensão de 16x16 *pixels*, assim como no diagrama resumo da figura 18.

Figura 18 – Parâmetros do Fatiamento dos Frames

#### 3.2.2 Captura e Preparação

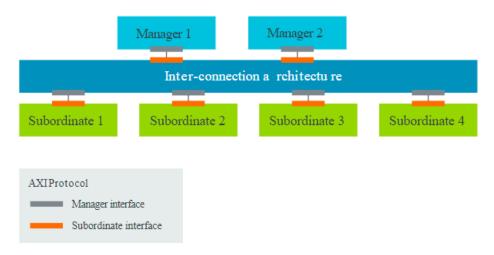

Com o intuito de priorizar a detecção de movimento em si, a etapa de captura e tratamento das imagens foi abstraída da máquina de estado proposta. Todavia, o programa base em software executa uma thread que captura e trata o par de imagens de forma semelhante à descrita na seção 3.1.1, mudando apenas a fonte de captura de uma câmera IP para a webcam embutida no notebook que executa o programa. Na PYNQ, a captura e o tratamento das imagens é de responsabilidade do processador ARM que, embarcado com um sistema operacional Linux, também executa a thread descrita na seção 3.1.1, mas envia os pixels das imagens capturadas para o FPGA através de um barramento AXI, descrito em 3.6.1.

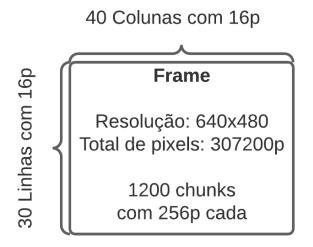

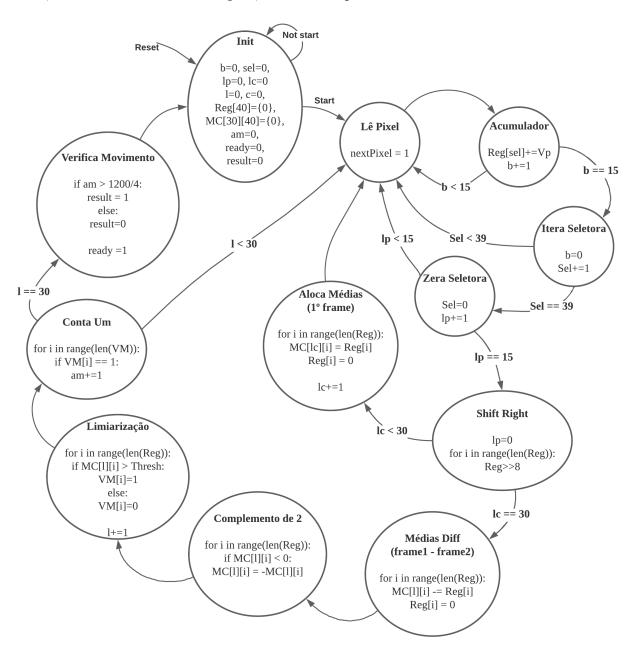

Com a captura dos quadros resolvida em *software* e considerando que a cada ciclo completo da máquina de estados um novo par de imagens é capturado e transformado

para escala de cinza, o algoritmo, em seu primeiro estado, aloca espaço em memória e atribui zero às variáveis de controle e aos registradores da FSM, assim como apresentado na figura 19.

Figura 19 – Estados: Init

Ainda da figura 19, observa-se que a FSM possui dois sinais para controlar os procedimentos de inicialização (start) e reinicialização (reset) do algoritmo. O sinal reset é uma interrupção que, independente do estado atual, envia a FSM para o estado Init. Já o sinal start funciona apenas no estado Init, enviando a FSM para o estado Lê pixel.

#### 3.2.3 Acumulo das intensidades por quadrante

Existem 3 variáveis fundamentais para orquestrar o funcionamento desta etapa da FSM, sendo elas:

- Contador de bytes  $(0 \le b < 16)$

- Seletora de registradores  $(0 \le Sel < 40)$

- Contador de linhas de pixels  $(0 \le l_p < 16)$

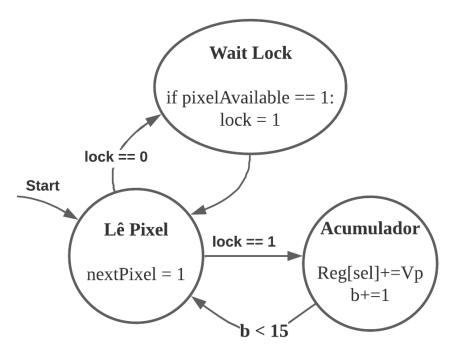

O contador de bytes b é iterado em uma unidade a cada valor de pixel,  $V_p$ , lido. A seletora de registradores Sel é iterada em uma unidade a cada 16 bytes lidos, ou seja a cada linha de um chunk lida. Já o contador de linhas de pixels  $l_p$  é iterado em uma unidade a cada 640 bytes, ou seja, a cada linha de pixels completa da imagem. Além disso, a máquina de estados utiliza um vetor com 40 posições para armazenar o somatório do valor dos pixels em uma determinada região, definida pela variável Sel. Neste contexto, a FSM lança mão sobre 4 estados que trabalham em um laço de leitura e acumulo dos pixels, como observado na figura 20.

O estado Lê Pixel, levanta a flag nextPixel indicando à thread de captura que a FSM está pronta para receber o valor do próximo pixel. Em seguida, no estado Acumulador, o valor do pixel lido  $(V_p)$  é acumulado na posição Sel no vetor Reg[Sel]. A

Figura 20 – Estados: Lê Pixel, Acumulador, Itera Seletora e Zera Seletora

cada  $V_p$  acumulado, o contador de bytes b é incrementando em uma unidade. Até 16 pixels serem somados ao registrador Reg[Sel], referente ao chunk atual, a FSM oscila entre os estados  $\mathbf{L}\mathbf{\hat{e}}$   $\mathbf{Pixel}$  e  $\mathbf{Acumulador}$ . Contudo, ao completar a linha de 16 pixels do chunk atual, a seletora Sel é iterada em uma unidade no estado  $\mathbf{Itera}$   $\mathbf{Seletora}$  que, além disso, também zera o contador de bytes b. A seguir a FSM volta a oscilar entre  $\mathbf{L}\mathbf{\hat{e}}$   $\mathbf{Pixel}$  e  $\mathbf{Acumulador}$ , mas agora apontando para o registrador do próximo chunk.

Após acumular 640 pixels a seletora Sel soma um total de 39 unidades. Para tanto, no estado **Zera Seletora**, atribui-se valor nulo para variável Sel que retorna a posição do registrador Reg[Sel] ao primeiro chunk para começar o somatório da próxima linha. Além disso, ainda neste estado, o contador de linhas de pixels  $l_p$  é iterado em uma unidade. Ou seja, ao finalizar uma linha completa da imagem o algoritmo acumulou 16 pixels de comprimento para cada um dos 40 chunks no vetor Reg[Sel]. Desta forma, a FSM executa este laço de leitura e acumulo até alcançar 16 linhas de pixels completas  $(l_p)$  e mudar para o estado **Shift Right**, descrito adiante.

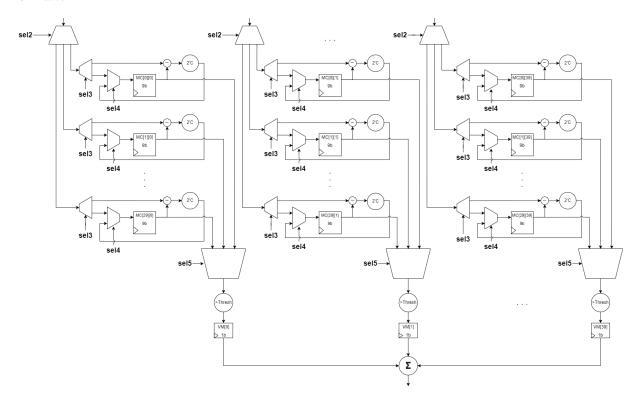

Em termos de um projeto RTL, esta etapa de leitura e acumulo de *pixels* pode ser representado pelo diagrama da figura 21. Em que um multiplexador controlado pela variável sel distribui os valores dos pixels que serão acumulados dentre as 40 posições do vetor de registradores Reg[40].

Figura 21 – Diagrama RTL: Leitura e Acumulo de pixels

#### 3.2.4 Valor médio do quadrante

Ao acumular os valores de intensidade de 16 linhas completas, cada uma das 40 posições do vetor Reg[40] guarda um montante do somatório de 256 pixels. Porém, como o interesse é sobre o valor médio das intensidades em cada região, o algoritmo executa, no estado **Shift Right** da figura 22, 8 deslocamentos a direita sobre estes montantes, o que equivale a dividir o valor acumulado por 256. A quantidade de pixels por quadrantes foi cuidadosamente escolhida visando simplificar as operações aritméticas envolvidas, por exemplo, substituindo as divisões por deslocamentos a direita o que acelera o cálculo das médias dos quadrantes. Além disso, em hardware, está operação é feita sobre os 40 registradores de forma paralela, em contraponto ao programa base em software que calcula a média das regiões de forma sequencial.

Ainda no estado **Shift Right**, o contador de linhas de *pixels*  $l_p$  é zerado e uma nova variável passa a ser considerada, o contador de linhas de *chunks*  $l_c$ . Se esta última for menor que 30, significa que a FSM ainda está processando o primeiro quadro e, para tanto, os valores médios dos *chunks* são armazenados em uma matriz chamada de MC[30][40] que possui 30 linhas e 40 colunas para suportar os 1200 *chunks* da primeira imagem.

No estado **Aloca Médias**, a variável  $l_c$  determina em qual linha da matriz MC[30][40] o valor médio dos 40 *chunks*, em Reg[40], serão armazenado. E, assim como no estado anterior, quando em *hardware*, este processamento é feito de forma paralela. Para tanto, a cada linha de *chunks* armazenadas em MC[30][40], a FSM incrementa  $l_c$  em uma unidade. Se  $l_c$  for igual a 30, conclui-se que a média de todas as regiões da primeira imagem já estão armazenada em MC[30][40] e que a segunda imagem começou a ser processada. Desta maneira, o algoritmo segue para o estado **Médias Diff** explicado na seção 3.2.5.

Figura 22 – Estados: Shift Right e Aloca Médias

Em termos de um projeto RTL, esta etapa de cálculo e armazenamento das médias dos quadrantes da primeira imagem pode ser representada pelo diagrama da figura 23. Em que o multiplexador controlado pela variável sel2, equivalente a  $l_C$ , determina em qual linha da matriz MC[30][40] as médias das intensidades por quadrante serão armazenadas. Além disso, na etapa em questão, o multiplexador controlado pela variável sel3 e o demultiplexador controlado pela variável sel4 estão configurados de tal forma a deixar o sinal da média recém calculada ser armazenada diretamente em MC[30][40].

Figura 23 – Diagrama RTL: cálculo e armazenamento das médias dos quadrantes

### 3.2.5 Comparação e Limiarização

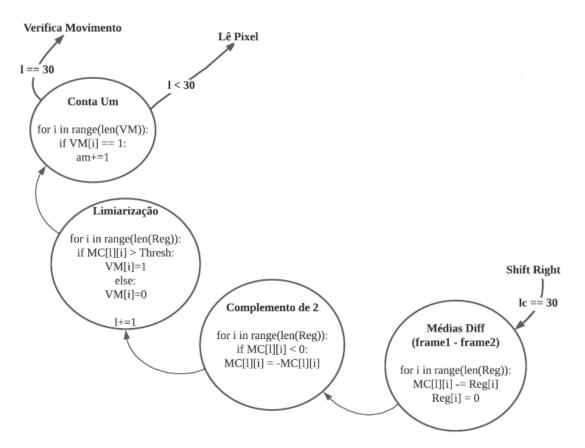

Figura 24 – Estados: Médias Diff, Complemento de 2 e Limiarização

Ao atingir  $l_c=30$ , a matriz MC[30][40] armazena a intensidade média dos 1200 quadrantes que dividem a primeira imagem. A partir daí, a FSM passa a calcular a média

das regiões da segunda imagem, comparando-as com aquelas da primeira. Neste contexto, em **Médias Diff** o algoritmo subtrai os valores contidos em MC[30][40], referente ao primeiro frame, com os valores do vetor Reg[40] que neste momento armazena as médias de 40 regiões do segundo frame. Assim, a variação de intensidade média das regiões de pixels é calculada e substituída na matriz MC[30][40]. Como o resultado desta subtração pode ser negativo, o estado **Complemento de 2** garante que todos os valores sejam positivos, mantendo apenas o módulo dos resultados.

No programa base em *software*, o módulo é calculado de forma tradicional, elevando a diferença ao quadrado e depois encontrando a raiz quadrada do valor. Contudo, visando reduzir o número de operações aritméticas para acelerar o sistema, na descrição de *hardware*, optou-se por representar os números em complemento de dois, modificando aqueles que indicassem 1 em seu bit mais significativo. Ou seja, mantendo os valores positivos e positivando os valores negativos.

Voltando para máquina de estados, logo que o módulo da variação dos *chunks* entre as imagens é calculado e positivado, o estado **Limiarização** compara este módulo a um limiar de sensibilidade atribuído pelo usuário. Se a variação for maior que o limiar, conclui-se que houve movimento naquele quadrante e, para tanto, a posição, referente ao *chunk* atual, do vetor de movimento VM[40] recebe 1. Caso contrário, recebe 0.

Nesta etapa da FSM existe um contador de linhas l que funciona de forma semelhante à variável  $l_c$  no estado Aloca Média, determinando em qual linha da matriz MC[30][40] a subtração entre o primeiro e o segundo frame deve ser armazenada. Vale ressaltar que em hardware, assim como nos estados Shift Right e Aloca Médias, as operações realizadas entre as 40 posições dos registradores Reg[40] e das 40 colunas de MC[30][40] em Médias Diff, Complemento de 2 e Limiarização ocorrem de forma paralela. Além disso, a cada Limiarização o contador de linhas l é incrementado em uma unidade. Por outro lado, no estado Conta Um, o algoritmo incrementa o acumulador de movimento am em uma unidade para cada posição de VM[40] que for igual a um, de forma sequencial. Ainda no estado Conta Um, enquanto l não atingir um valor total de 29 unidades, a FSM volta para o estado Lê Pixel, indicando que o segundo quadro ainda está sendo processado. Caso contrário, o próximo estado será Verifica Movimento, explicado na seção 3.2.6.

Em termos de um projeto RTL, esta etapa de comparação e limiarização entre as regiões do primeiro e do segundo frame pode ser representada pelo diagrama da figura 25. Em que o multiplexador controlado pela variável sel2, agora equivalente a l, determina qual linha da matriz MC[30][40] será processada. Além disso, na etapa em questão, o multiplexador controlado pela variável sel3 está configurado para encaminhar o valor médio das regiões do segundo frame até a subtração com o valor médio das regiões do primeiro frame, armazenados em MC[30][40], bem como, o demultiplexador controlado

pela variável sel4 esta configurado de tal forma a substituir o resultado da subtração já positivado em MC[30][40]. A seguir o demultiplexador controlado pela variável sel5, também equivalente a l, determina qual das linhas da matriz MC[30][40], agora com a variação média das intensidades entre o par de imagens, que será comparada ao limiar de detecção atribuído pelo usuário. O valor binário resultante de cada uma das colunas comparadas é armazenado no registrador VM[40] e esses valores são somados e acumulados em am.

Figura 25 – Diagrama RTL: Comparação e Limiarização

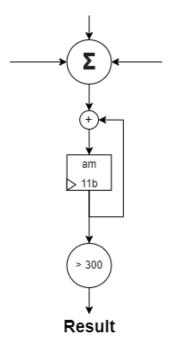

#### 3.2.6 Verificador de Movimento

Após a comparação entre todos os *chunks* das duas imagens, o acumulador de movimento am armazena um inteiro que pode ir de 0 a 1200, indicando algo entre: total ausência de movimento ou movimento em todos as regiões. Seguindo a métrica implementada no **Produtor de Frames**, o estado **Verifica Movimento** busca ao menos 25% de *chunks* com movimento para levantar a *flag result* = 1 que engatilha a captura de um trecho de vídeo proveniente do fluxo de imagem da câmera, chamado aqui de evento. No entanto, se am indicar um valor menor que 300 o estado **Verifica Movimento** abaixa a *flag result* = 0 e nada acontece. Porém independente do valor de *result*, o estado **Verifica Movimento** levanta a *flag ready* = 1, indicando que o algoritmo de detecção de movimento terminou de comparar um par de imagens. Finalmente, a FSM volta para o

estado  $\mathbf{Init}$ , assim como observado na figura 26, reiniciando as variáveis e esperando pelo próximo start.

Figura 26 – Estado: Verifica Movimento

Em termos de um projeto RTL, esta etapa de Verificação de movimento pode ser representada pelo diagrama da figura 27.

Figura 27 – Diagrama RTL: Verificação de movimento

### 3.2.7 Máquina de Estados e RTL Completos

As figuras 28 e 29 apresentam, respectivamente, a máquina de estados e o diagrama RTL, analisados nas últimas seções, em sua completude.

Figura 28 – FSM Completa

Figura 29 – RTL Completo

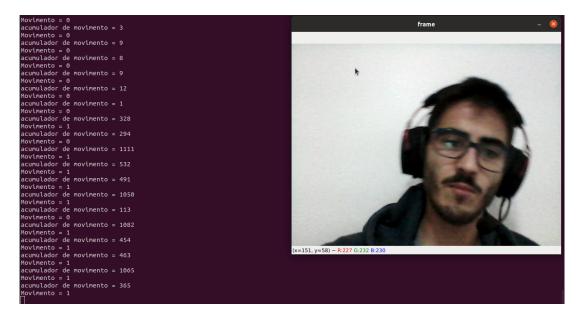

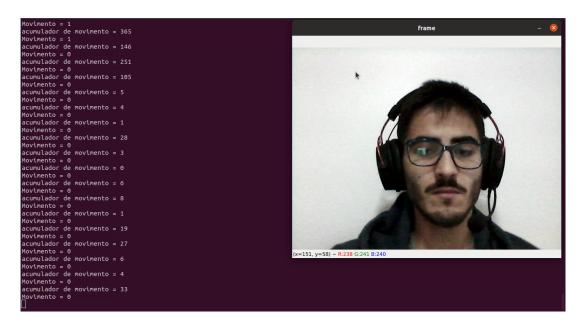

# 3.3 Validação da FSM em Python

Tendo em vista a máquina de estados descrita na seção 3.2, em um primeiro momento, descreveu-se uma aplicação Python, disponível em (FREITAS, 2021a), para validação em software do algoritmo proposto. Esta aplicação Python possui duas classes chamadas de FrameCapture e MotionDetector que, quando instanciadas como objetos, inciam duas threads computacionais. A primeira é responsável pela recepção, exibição e tratamento dos frames disponibilizados por uma fonte de captura, tal qual um câmera ou um arquivo de vídeo em mp4. A segunda thread opera a máquina de estados proposta

através do objeto *MotionDetector*, em que cada um de seus métodos representa um estado da FSM. Além disso, a aplicação em Python coloca um FIFO entre os objetos para enfileirar as imagens recebidas pelo *FrameCapture* que posteriormente serão processadas pelo *MotionDetector*.

Em primeiro momento, a FSM em Python foi validada em tempo real utilizando uma webcam com resolução de 0.3 Megapixel e capturando imagens com dimensões de 640x480p. Os resultados dessa validação estão descritos na seção 4.1. Em um segundo momento, a aplicação utilizou um vídeo de teste, disponível em (FREITAS, 2022g), como fonte de captura para termos de comparação com a simulação comportamental do algoritmo em VHDL (vide seção 3.5). Os resultados dessa comparação estão descritos na seção 4.3.

Para os dois testes descritos no parágrafo anterior, o programa foi executado em um processador Intel i5-10210U Quad Core com 8Gb de memória RAM, rodando um sistema operacional Ubuntu 20.04.

## 3.4 Descrição de Hardware da FSM

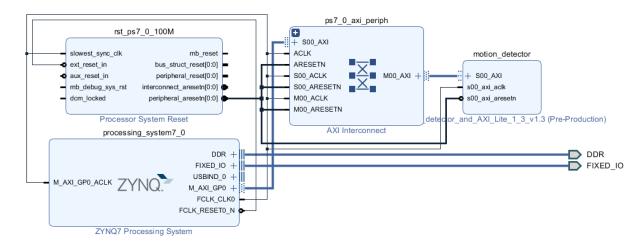

Tendo a máquina de estados validada em *software*, descreveu-se o algoritmo em VHDL através do *framework* Vivado que possui um conjunto de ferramentas para síntese e análise de projetos de linguagem de descrição de *hardware* oferecida pela Xilinx (XILINX, 2022). O código de referencia da FSM em VHDL está disponível em (FREITAS, 2022e).

Baseado nos estados, variáveis e sinais descritos na seção 3.2, a FSM em VHDL foi estruturada dentro de uma entidade que possui 5 entradas, dentre as quais, um bit para o sinal de *clock*, um bit para o sinal de *start*, um bit para o sinal *reset*, um bit para o sinal indicador de *pixel* disponível, chamado de *pixelAvailable*, e um barramento com um byte de comprimento para receber o valor dos *pixels*, chamado de *pixelValue*. Além disso, esta entidade possui 3 saídas, um bit para o sinal que pede pelo próximo *pixel*, chamado de *nextPixel*, um bit para o sinal que indica quando a detecção de movimento terminou, chamado de *ready* e um bit para o sinal que indica o resultado da detecção de movimento, chamado de *result*.

O comportamento desta entidade, foi descrito através de três processos independentes, sendo dois síncronos, ou seja orquestrados pelo sinal de *clock*, e um assíncrono. O primeiro processo síncrono é sensível apenas ao *clock* e é responsável pela mudança de estados, em que o estado atual recebe o próximo estado, se o sinal *reset* for zero, caso contrário o estado atual aponta para o estado *Init* (vide seção 3.2.2). Já o segundo processo síncrono é sensível aos 5 sinais de entrada, bem como, ao estado atual e tem como responsabilidade lidar com as variáveis de controle e com os registradores da FSM, ou seja, a cada ciclo de *clock* e, também, a depender do estado atual e dos sinais *start*,

reset, pixel Available e next Pixel, este processo atualiza as variáveis de controle b, Sel,  $l_P$ ,  $l_C$ , l e am, bem como, atualiza os registradores Reg[40], MC[30][40] e VM[40], melhor descritos na seção 3.2. O processo assíncrono, por sua vez, é sensível tanto ao estado atual, quanto aos sinais de entrada e também às variáveis de controle. Seu objetivo é determinar qual será o próximo estado baseado na relação das variáveis da sua lista de sensibilidade.

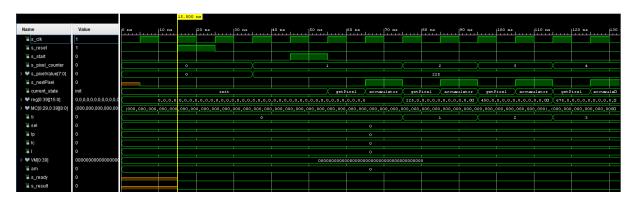

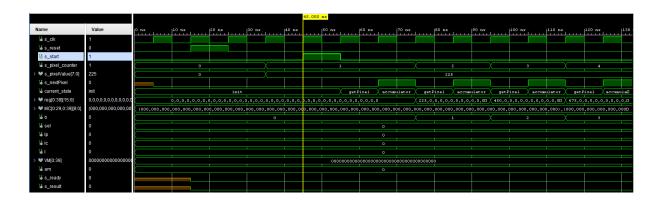

## 3.5 Simulação Comportamental da FSM

O Vivado disponibiliza uma ferramenta de simulação comportamental para testar a entidade descrita na seção anterior. Para tal procedimento, escreve-se um outro código também em VHDL, disponível em (FREITAS, 2022d), conhecido como *Testbench* (TB), que instancia a entidade como um componente, opera seus sinais de entrada e verifica seus sinais de saída ao longo do tempo para validar o algoritmo proposto.

#### 3.5.1 Arquivo de *Pixels*

Para a simulação é necessário um vídeo de teste que alimentará o algoritmo com os valores de seus pixels. Para tanto, um vídeo com 3 segundos de duração foi gravado a 6 fps, acumulando um total de 18 frames em escala de cinza, disponível em (FREITAS, 2022g). Considerando que cada frame possui dimensão de 640x480p, o vídeo é composto por um total de 5.529.600 pixels. Com o intuito de disponibilizar este vídeo à ferramenta de simulação do Vivado, foi necessário criar um arquivo de texto, em que cada uma de suas linhas registra um byte referente a um pixels do video de teste. Este arquivo de texto foi gerado com auxilio de um programa em Python, disponível em (FREITAS, 2022f), que utiliza do capturador de video da OpenCV, vide (OPENCV, 2021a), e as funções de manipulação de arquivos, nativas do Python, para operar a escrita dos pixels no arquivo de texto, que está disponível em (FREITAS, 2022c).

#### 3.5.2 Testbench

Além de instanciar a entidade como componente, no TB disponível em (FREITAS, 2022d), um processo síncrono foi declarado para abrir e ler o arquivo de pixels e, a cada ciclo de *clock*, inserir um novo byte no barramento *pixelValue* do componente que opera a FSM. Não obstante, fora do processo de leitura do arquivo de *pixels*, os sinais de *start* e reset são acionados para garantir a inicialização e a reinicialização da FSM. Vale ressaltar que o *clock* foi declarado no TB como um sinal auxiliar com período de 10 ns. Além disso, pelo fato do processo de leitura do arquivo de *pixels* estar sincronizado em 100 Mhz, assim como o componente que opera a FSM, o sinal *pixelAvailable* está sempre acionado como verdadeiro. Os resultados da simulação comportamental da FSM estão apresentados na seção 4.2.

### 3.6 Protótipo na plataforma PYNQ-Z2